半導體矽智財,又稱IP 核(Intellectual Property core)是一段具有特定電路功能的硬體描述語言程序,常常被用於數字電路中。該程序與集成電路工藝無關,可以移植到不同的半導體工藝中去生產集成電路晶片,從而幫助開發人員減少工作量,並加快產品上市。

1G 網管冗餘交換機IP核— 可用於Xilinx Vivado

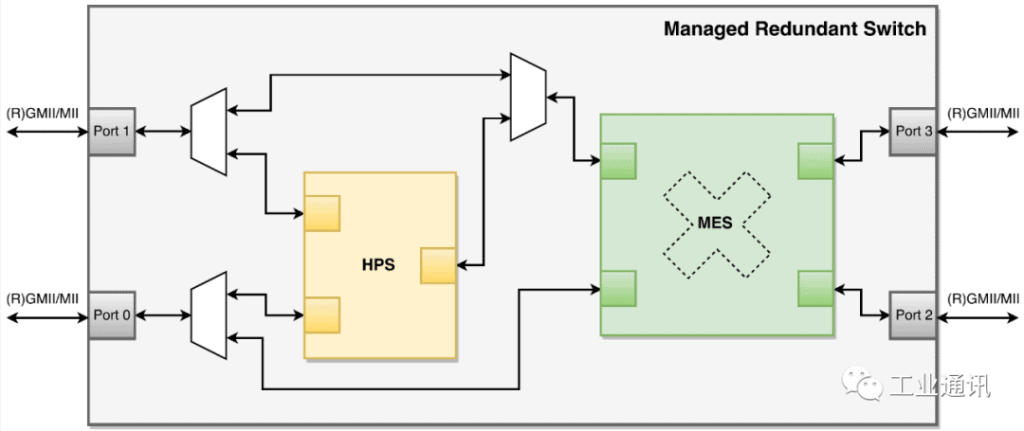

網管冗餘交換機IP核(MRS)是虹科HSR-PRP交換機(HPS)和網管以太網交換機(MES)IP核的組合,具有冗餘的以太網交換功能。MES模塊是一個無阻塞交叉開關矩陣,允許在所有端口之間進行連續傳輸。它實施存儲轉發的交換方法,以完全滿足以太網標準策略關於轉發每個幀之前校驗幀的完整性。另一方面,HPS模塊在所需的端口中引入了HSR和PRP冗餘功能。HSR 的切換方法是Cut-Through(直通)。因此,MES和HPS的組合提供了最高的性能和與標準的最大相容性。

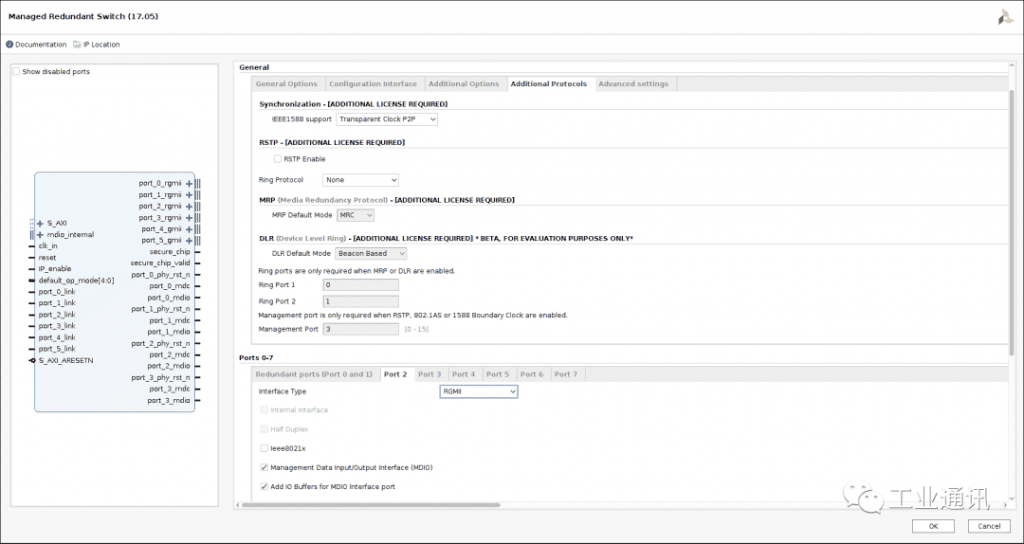

網管冗餘交換機可以利用新的Xilinx Vivado 工具輕鬆集成到用戶的FPGA 設計中,該工具允許在圖形用戶界面中使用IP 內核並以簡單的方式配置IP 參數。

以下Xilinx FPGA系列可以支持虹科MRS IP核:

▪ 6 系列(Spartan、Virtex)

▪ 7 系列(Zynq、Spartan、Artix、Kintex、Virtex)

▪ 超大規模(Kintex、Virtex)

▪ Ultrascale+(Zynq MPSoC、Kintex、Virtex)

HK 網管冗餘交換機IP核的主要功能

# 接口

▪ 全雙工10/100/1000 Mbps以太網接口

▪ 半雙工10/100 Mbps以太網接口

▪ 全雙工10 Gbps以太網接口(開發中)

▪ 可配置的 3至 16個以太網端口

▪ MII/ GMII/ RGMII/ SGMII/ QSGMII物理層設備(PHY)接口

▪ 每個端口支持不同的數據速率

▪ 銅纜和光纖介質接口:10/100/1000Base-T,100Base-FX,1000Base-X

# 交換

▪ 具有自動 MAC地址學習和老化的動態 MAC表(最多2048個條目)

▪ 靜態 MAC表(最多2048個條目)

▪ 巨型幀管理

▪ 基於以太網的交換

▪ 入口端口鏡像

▪ 廣播/多播風暴防護

▪ 每端口速率限制(廣播、多播和單播流量)

# 流通管理

▪ 多播幀過濾

▪ 交換端口掩碼:用戶定義的幀到具體端口的轉發

▪ 基於端口的VLAN支持

▪ 服務質量(QoS):優先級(PCP-802.1p,DSCP TOS,以太類型)

▪ IEEE 802.1X EAPOL硬體處理

▪ DSA(分佈式交換體系結構)標記:使用 DSA的理想情況是以太網交換機支持“交換機標籤”

# 組態

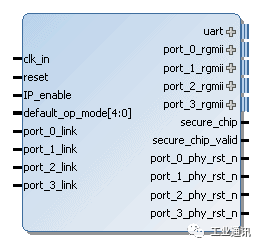

▪ MDIO,UART,AXI4-Lite或CoE(以太網配置)管理接口

▪ 以太網配置(COE):透過連接到CPU的同一以太網鏈路全面訪問內部寄存器

▪ 購買IP核時提供驅動程序

# 冗餘協議

▪ RSTP(需要軟體堆棧)

▪ MRP(不需要軟體堆棧)

▪ DLR(不需要軟體堆棧)

▪ HSR(不需要軟體堆棧)

▪ PRP(不需要軟體堆棧)