IP核(Intellectual Property core)是一段具有特定電路功能的硬體描述語言程序,常常被用於數字電路中。該程序與集成電路工藝無關,可以移植到不同的半導體工藝中去生產集成電路晶片,從而幫助開發人員減少工作量,並縮短產品上市時間。

虹科針對不同的應用和領域開發了一系列以太網交換IP,因而用戶可以將不同IP的特徵進行組合以獲得每種情況的最佳解決方案。本文就帶你了解虹科1G HSR/PRP交換機IP核。

什麼是HSR&PRP?

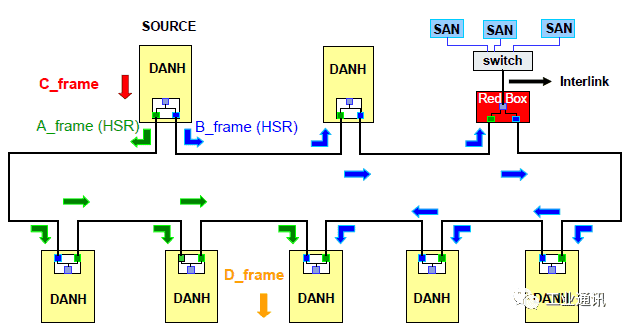

HSR和PRP是兩項相容性佳、易於使用的冗餘協議,其所屬的國際標準為IEC 62439,並已在電力行業得到廣泛使用和驗證。隨著網路拓撲越來越複雜,列車、工控甚至互聯網等行業對網路可靠性傳輸的需求不斷提升,這兩種能夠提供零切換延遲時間、在故障情況下不丟失幀的協議漸漸有了更廣闊的應用。也正是因為如此,虹科推出了HSR/PRP IP核,來幫助用戶開發相關產品。

虹科 1G HSR/PRP IP核

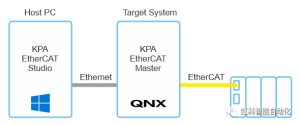

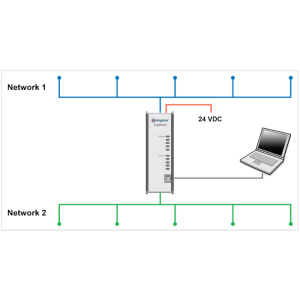

虹科電子— HSR/PRP 交換機 IP Core 是一個完整的硬體解決方案,可實現高可靠性無縫冗餘協議和並行冗餘標準,並能夠在低成本的 FPGA 上實現。它透過硬體來交換幀以提供很高的交換速度,同時也是實現變電站自動化的過程總線和機架間總線的最大允許使用年限和數據完整性所必需的。它是針對能源市場設備的一種靈活解決方案,該設備將連接到 HSR 環、PRP 局域網或在IEC 61850的環境下起到網橋的作用。

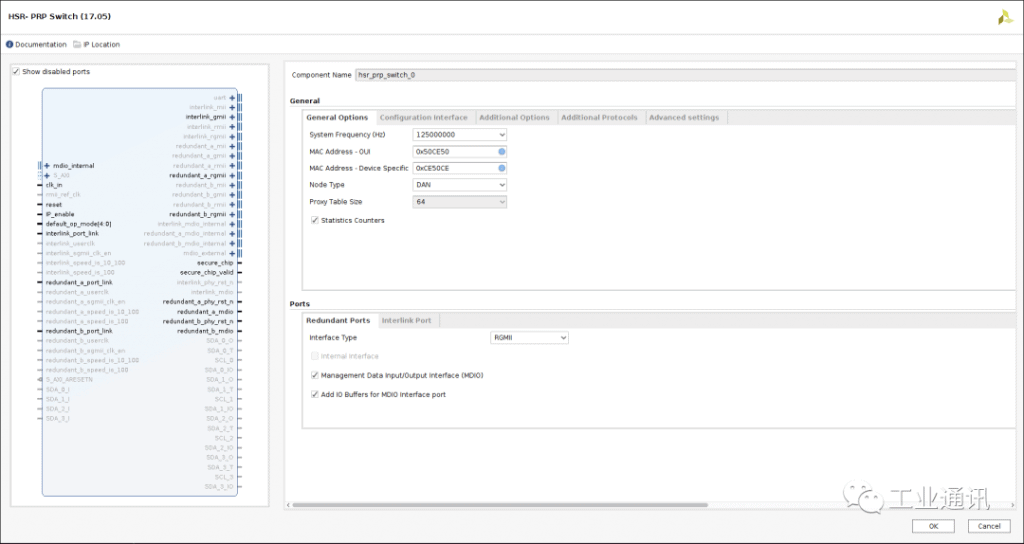

用於Xilinx Vivado工具的 虹科HSR-PRP交換機IP Core

以下 Xilinx FPGA 系列支持虹科 HSR-PRP IP Core:

- 6系列(Spartan,Virtex)

- 7系列(Zynq,Spartan,Artix,Kintex,Virtex)

- Ultrascale(Kintex,Virtex)

- Ultrascale +(Zynq MPSoC,Kintex,Virtex)

透過利用新的 Xilinx Vivado 工具,虹科 HSR-PRP 交換機 IP 核可以輕鬆集成到您的 FPGA 設計中,該工具允許在圖形用戶界面中使用該 IP 核,並以簡便的方式配置 IP 參數。

關鍵特性

1、# 接口

▪ 全雙工10/100/1000 Mbps以太網接口

▪ MII/RMII/GMII/RGMII/SGMII/QSGMII物理層設備(PHY)接口

▪ 每個端口支持不同的數據速率

▪ 銅纜和光纖介質接口:10/100/1000Base-T,100Base-FX,1000Base-X

2、# 交換

▪ 處理體系結構專用於HSR/PRP,千兆以太網的轉發延遲為500ns

▪ 全硬體解決方案,無需片上微處理器或軟體堆棧

▪ 已經過優化,幾乎不需要邏輯資源,從而可以在低成本FPGA組件上實現

▪ 巨型幀管理

3、# 冗餘與時間同步

▪ 可用於實現終端節點 DAN、RedBox 或 QuadBox 功能

▪ 帶有單個標誌,可以透過軟體在 PRP 和 HSR 模式之間切換

▪ 包括集成的每個端口的完整統計訊息和錯誤寄存器(網路監督)

▪ 支持與 SoC-e 1588 IP內核結合的 IEEE 1588-2008 v2

4、# 組態

▪ MDIO、UART、AXI4-Lite 或 CoE(以太網配置)管理接口

▪ 以太網配置(COE):透過連接到 CPU 的同一以太網鏈路全面訪問內部寄存器

▪ 購買IP核時提供驅動程序

5、# 可訂制功能

▪ 節點表大小

▪ 每個端口的轉發隊列大小獨立

▪ 冗餘和互連端口中的IEEE1588v2 P2P透明時鐘

▪ 可擴展的複制/循環丟棄表

▪ VLAN 優先級支持

▪ 透過 AXI4-Lite、MDIO、UART或CoE(以太網配置)訪問內部寄存器

▪ 具有集成SAN代理的RedBox模式

▪ IEEE 1588v2 普通時鐘、混合時鐘和邊界時鐘