在本篇文章中,我們將...

Read MoreMTSN IPcore

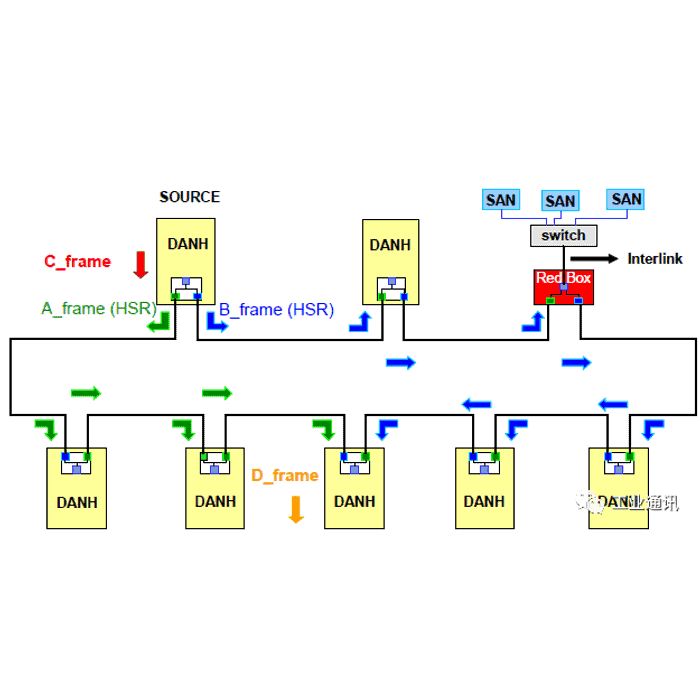

全面的TSN開發方案,能夠實現多種TSN協定規範

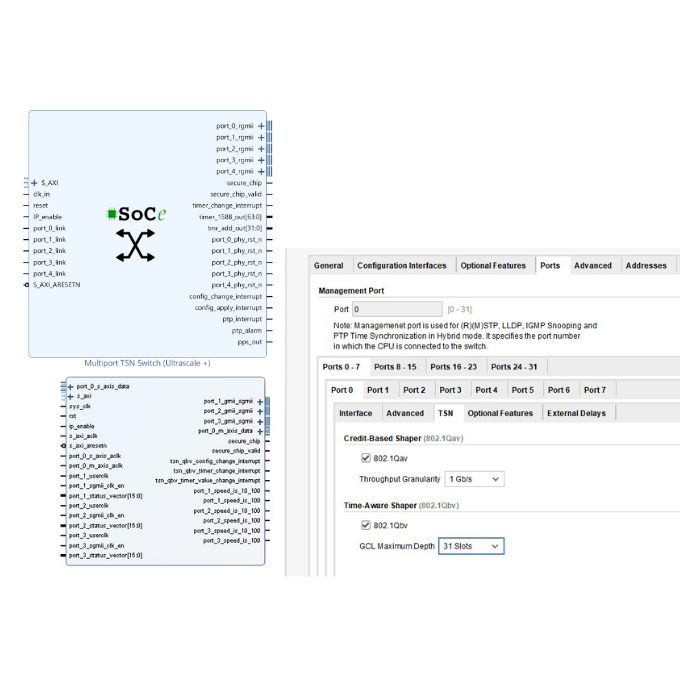

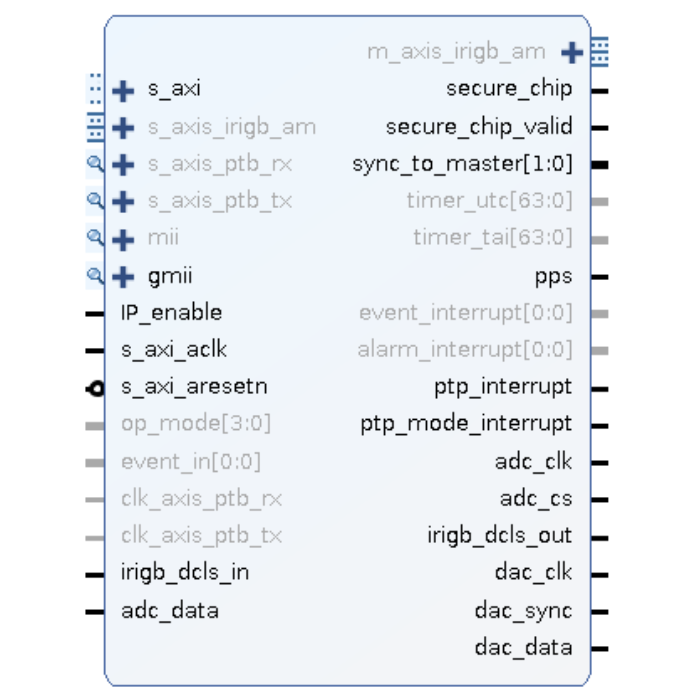

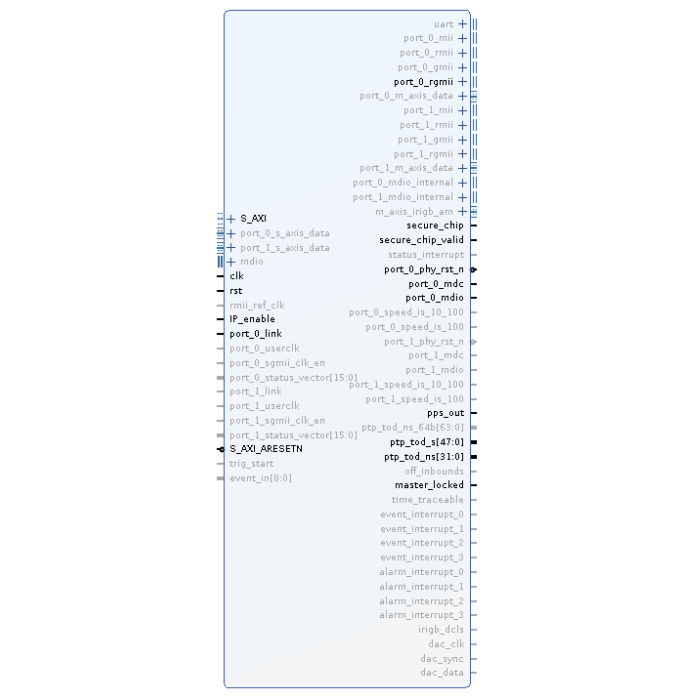

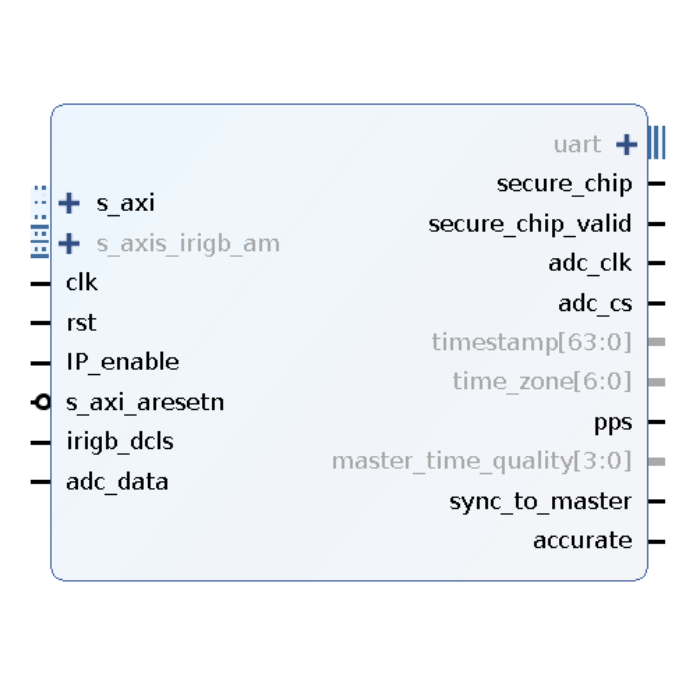

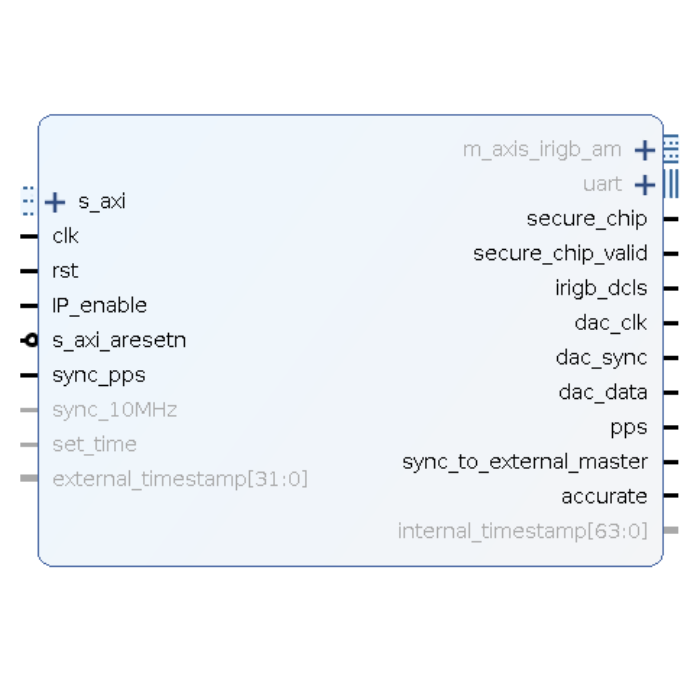

MTSN IP核是一個靈活的HDL代碼,可以生成TSN端點或TSN橋接實現。該IP提供了一組豐富的通用參數,以獲得最佳的功能資源權衡。由於Vivado IPI提供了GUI介面,因此可以在VHDL級別或以圖形方式配置這些通用專案。

- 多種PHY介面可選:MII/RMII/GMII/RGMII/SGMII/QSGMII

- 交換能力:全雙工10/100/1000 Mbps乙太網介面;最多可達32端口,每個端口支援不同的數據速率

- IP核配置端口:4 種配置管理端口