1G非網管乙太網交換機IP Core – 高效工業網路解決方案

功能概述:

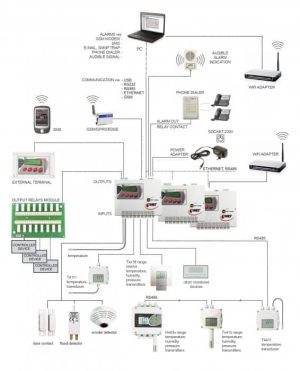

1G非網管乙太網交換機IP核為工業網路提供隨插即用的解決方案,具備無阻塞交叉開關矩陣和IEEE 1588 V2透明時鐘功能。支援Xilinx FPGA,靈活配置端口數量和緩衝區長度,實現高性能與資源優化的平衡,適合低延遲和高同步精度需求的應用。

分類: 無線通訊 標籤: 1G 乙太網交換機, IEEE 1588 V2, Xilinx FPGA 支援, 乙太網交換機 IP 核, 低延遲網路, 工業 FPGA 設計, 工業乙太網, 時間同步網路 (TSN), 非網管乙太網交換機, 高性能乙太網交換

描述

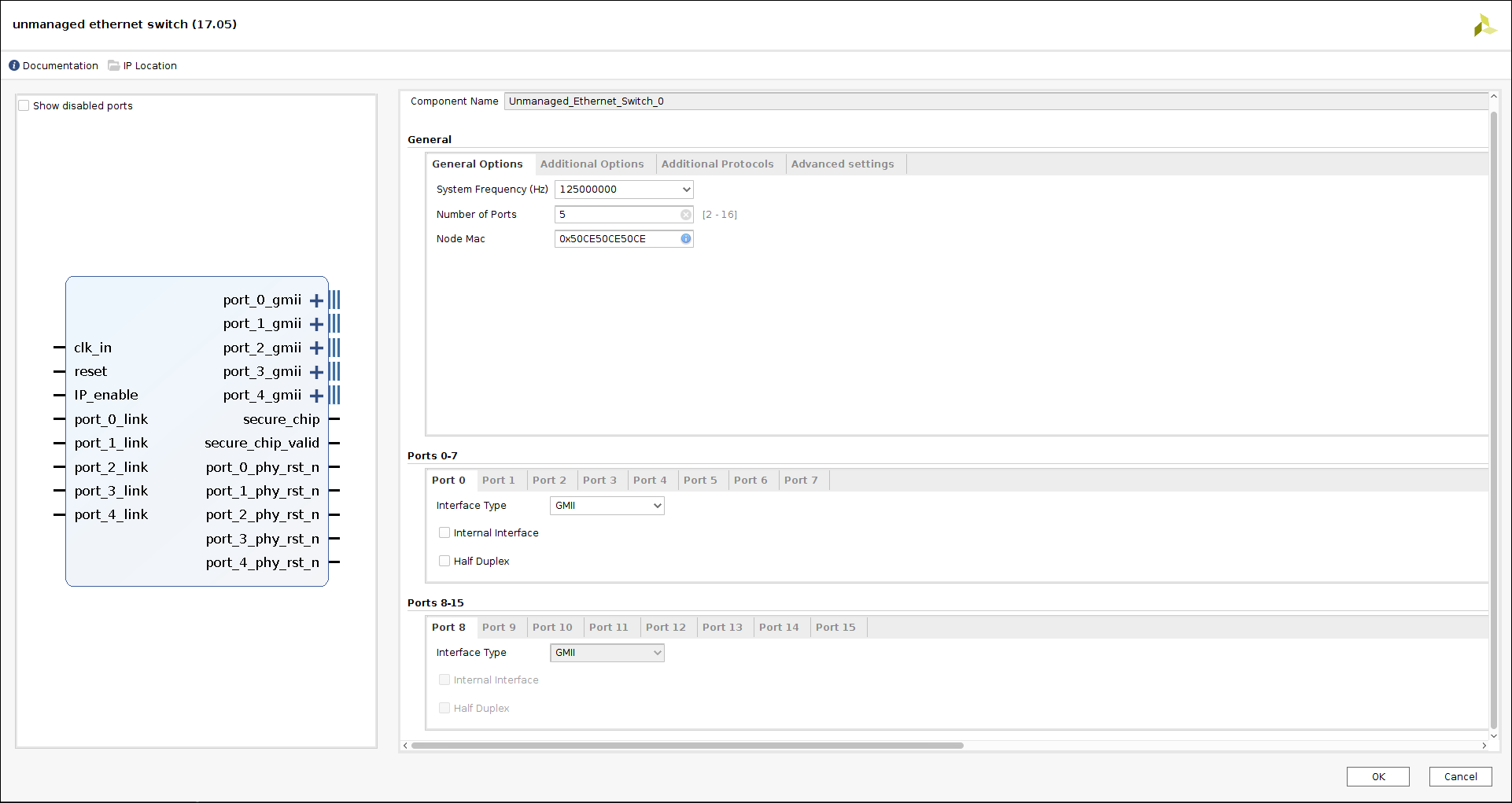

非網管乙太網交換機IP核(UES) 在可配置設備上實現了隨插即用的乙太網交換。它不需要外部配置,旨在使用最少的資源解決最大的輸送量。

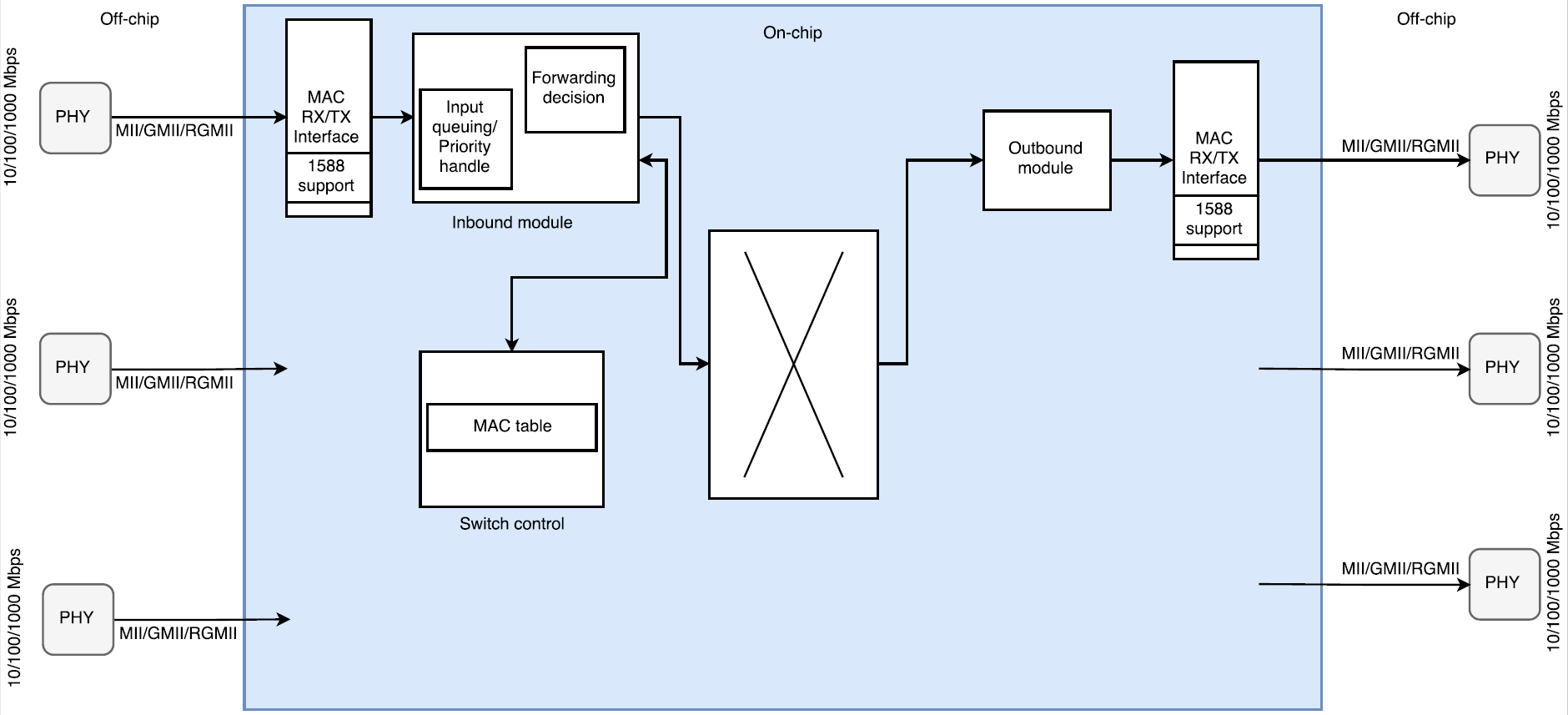

該交換機實現了一個無阻塞交叉開關矩陣,該矩陣允許所有端口之間進行線速通訊。交換機在轉發每個幀之前先對其進行緩存和驗證。然而,等待時間已被最小化到納秒級。此外,UES支援IEEE 1588 V2透明時鐘功能。該功能可糾正引入交換機產生的錯誤的PTP幀,從而使IEEE 1588同步設備之間的互連保持最高水準的準確性。

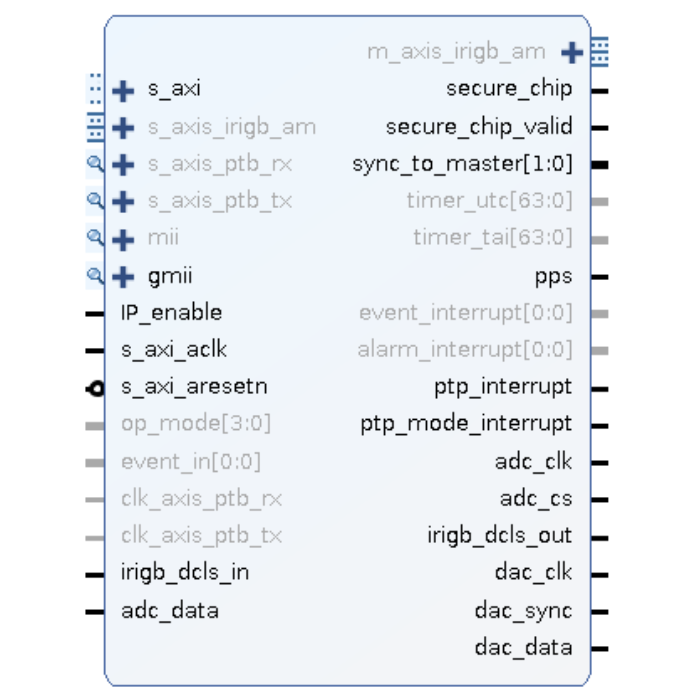

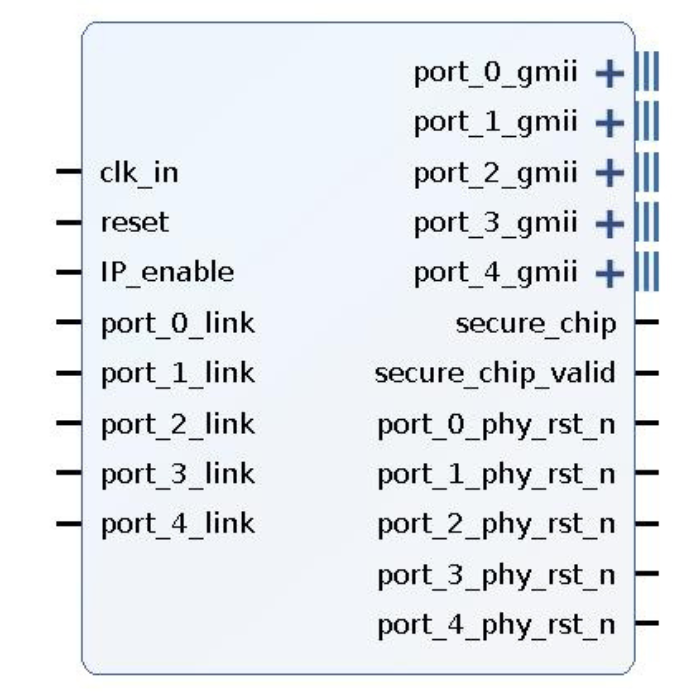

UES是實現基於乙太網的工業網路的理想乙太網交換機IP。它為乙太網PHY設備提供MII/GMII/RGMII本機介面,並且可以與Xilinx IP結合使用,以在其他介面中支援RMII或SGMII。它還支援將AXI4-Stream介面連接到其他不具有MAC基介面的IP內核。

支援的Xilinx FPGA系列:

- 7-Series (Zynq, Spartan, Artix, Kintex, Virtex)

- Ultrascale (Kintex, Virtex)

- Ultrascale+ (Zynq MPSoC, Kintex, Virtex)

- Versal ACAP

通過利用新的Xilinx Vivado工具,可以將UES 輕鬆集成到您的FPGA設計中,該工具允許在圖形化使用者介面中使用IP內核並以簡便的方式配置IP參數。

非網管乙太網交換機IP核的主要功能:

- 隨插即用:無需配置

- 高性能:實現端口之間的全交叉矩陣以實現最大輸送量

- 快速:由於SoC-e專有的MAC位址匹配機制,大大縮短了延遲時間

- 高效:經過優化,僅需很少的邏輯資源即可在低成本FPGA器件上實現

- 靈活:完全可擴展且可配置,以獲得最佳的功能-尺寸平衡。以下參數設計員可用:

- 端口數量:可配置的3至16個乙太網端口

- 緩衝區佇列長度

- IEEE透明時鐘功能

- 自動:MAC位址學習和老化(預設情況下,存儲容量為2048個MAC位址)。