IEEE 1588v2無CPU時鐘同步解決方案 – 1588 Tiny IP Core

功能概述:

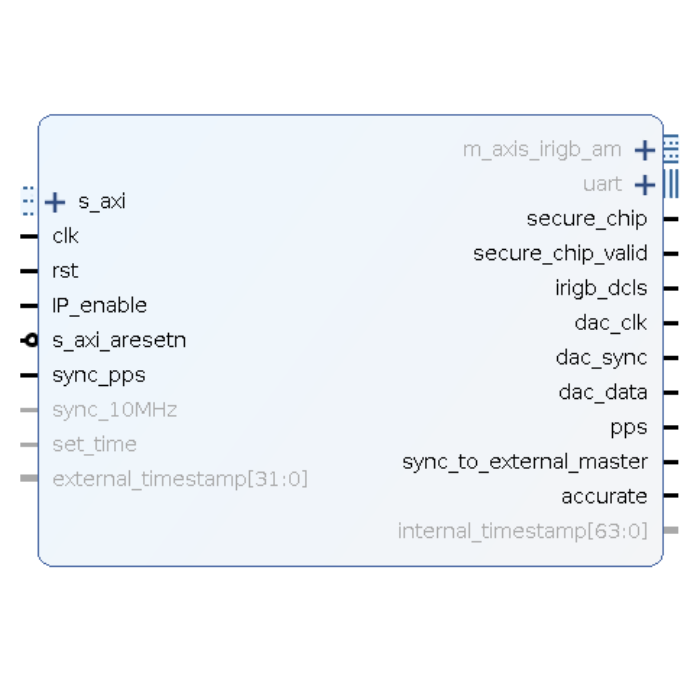

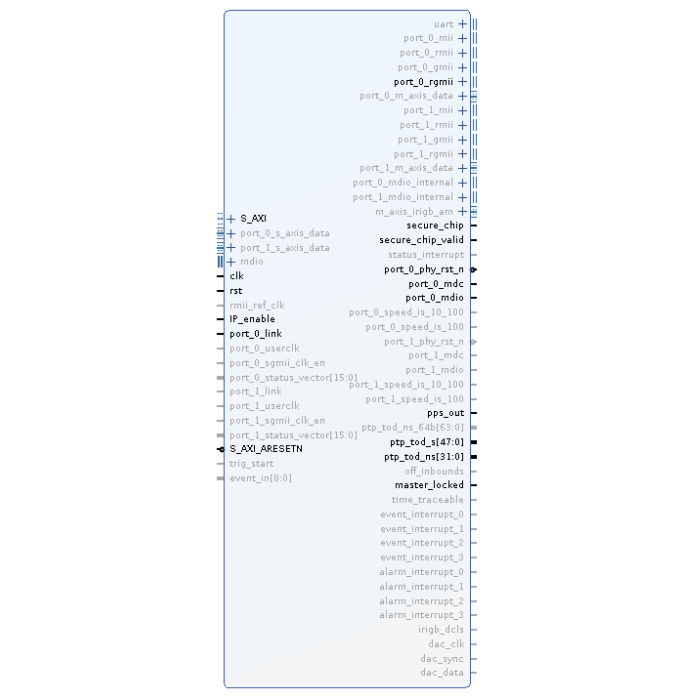

1588 Tiny是一款專為Xilinx FPGA設計的IEEE 1588-2008 V2從站硬體時鐘同步IP內核。它能夠提供精準的時間戳記和時鐘同步,不需要依賴嵌入式處理器或通用乙太網MAC,為資源受限的設備提供高效的IEEE 1588功能支援。該IP內核支援多種乙太網介面,包括MII、GMII、SGMII等,並可處理PTP報文,支援單端口和雙端口模式。它還可支援多種設定檔(如IEC 61850、電源設定檔等),適用於7-Series、Ultrascale、Ultrascale+及Versal ACAP等Xilinx FPGA系列。1588 Tiny與Xilinx Vivado工具無縫整合,使其易於配置並整合到FPGA設計中,確保在FPGA內部進行高精度的硬體時間同步。