精確時間基礎 是Xilinx FPGA的IEEE1588-2008 v2相容時鐘同步IP內核。它能夠準確地為IEEE 1588報文打上時間戳記,並提供相容的計時器。所有這些過程均由硬體模組執行。

精確時間基礎IP包含的元素:

- 硬體時間戳記單元(TSU):能夠準確地為IEEE 1588事件消息加時間戳記,並提供具有亞微秒精度的可調計時器。TSU有兩種版本:PTB TSU和PTBLite TSU。

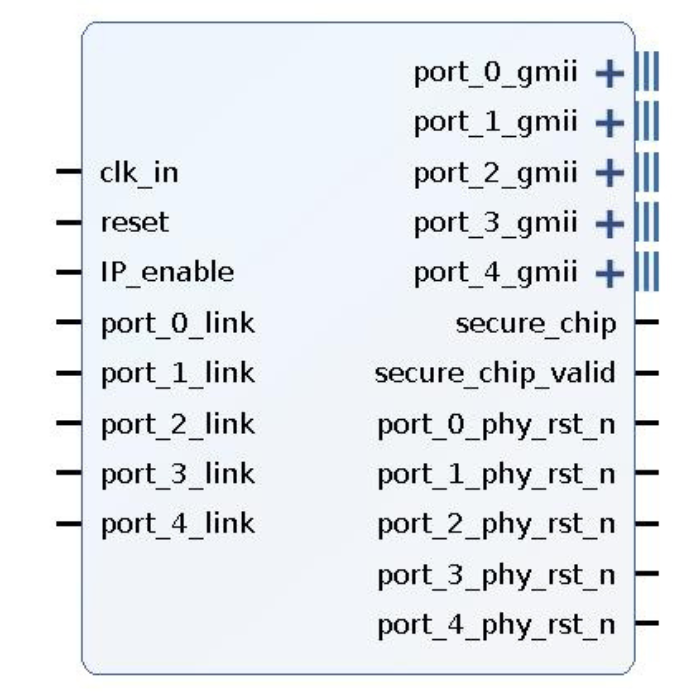

- PTB TSU:設計為連接到MAC和PHY之間的介質獨立介面([G] MII),解析所有乙太網幀並檢查哪些是IEEE 1588。

- PTBLite TSU:利用Zynq GMAC中的PTP解析器,以較少的FPGA資源提供TSU,但有一些限制。

- 兩種版本的TSU都可以使用內部可調計時器或從另一個TSU獲取計時器值,允許多個乙太網連接共用同一計時器。

軟體PTP參考設計:

SoC-e提供了Linux內核補丁,允許使用Linux PTP硬體時鐘(PHC)子系統訪問TSU。此外,還有開源LinuxPTP軟體堆疊的修改版本,模組化設計易於移植。

支援的Xilinx FPGA系列:

- 7-Series (Zynq SoC, Spartan, Artix, Kintex, Virtex)

- Ultrascale (Kintex, Virtex)

- Ultrascale+ (Zynq MPSoC, Kintex, Virtex)

- Versal ACAP

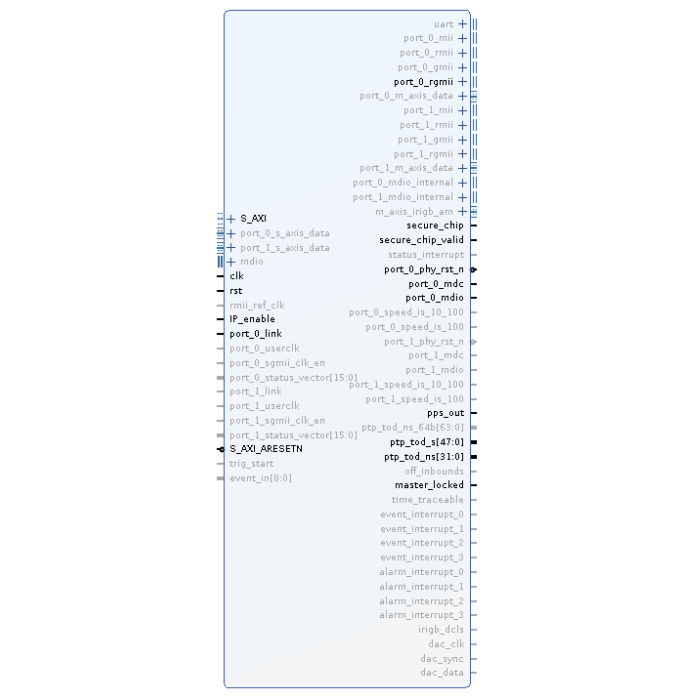

透過Xilinx Vivado工具,可以輕鬆整合到FPGA設計中,該工具允許在圖形化使用者介面中使用IP內核,並簡便配置IP參數。

精確時間基礎IP Core的主要功能:

硬體功能:

- 支援10/100/1000Mbps/AXI-Stream(用於10Gbps/25Gbps)介面

- 32位秒/32位納秒計數器

- 32位元亞納秒頻率調整

- 每秒一脈衝輸出

- 可選頻率輸出(1 KHz/2 KHz/4 KHz/8 KHz/16 KHz/32 KHz)

- 最低的FPGA資源利用率

- 警報生成

- 事件時間戳記記錄

軟體功能:

- 普通時鐘(主站和從站)操作

- 端到端和點對點延遲機制支援

- 支援乙太網(第2層)和IPv4(第3層)介面上的PTP

- VLAN支持

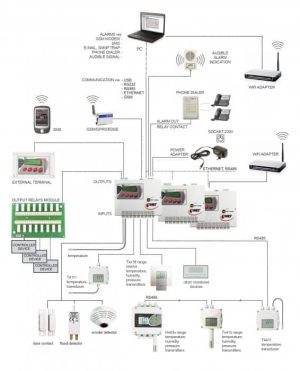

- 可結合HSR-PRP和網管乙太網IP內核使用

設定檔支援:

- 工業設定檔:預設、電源、電源實用程式IEC 61850-9-3、IEEE 802.1AS

- 汽車設定檔:IEEE 802.1AS通用PTP(gPTP)設定檔

- 企業設定檔/5G/電信設定檔:G.8265.1,G.8275.1和G.8275.2

IEEE 1588系統的最終精度取決於多個因素,包括本地時鐘頻率、資料鏈中的時間戳記位置等。以下圖示範商業Grandmaster設備和Zedboard Avnet Devopment Platfrom之間的PPS測量誤差,使用精確時間基礎進行硬體輔助時間戳記(+/-50 ns)。