HSR/PRP Switch IP Core - High Availability Ethernet Redundancy Solution

Function Overview:

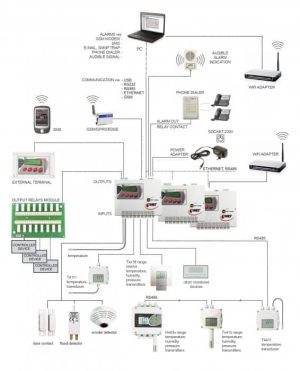

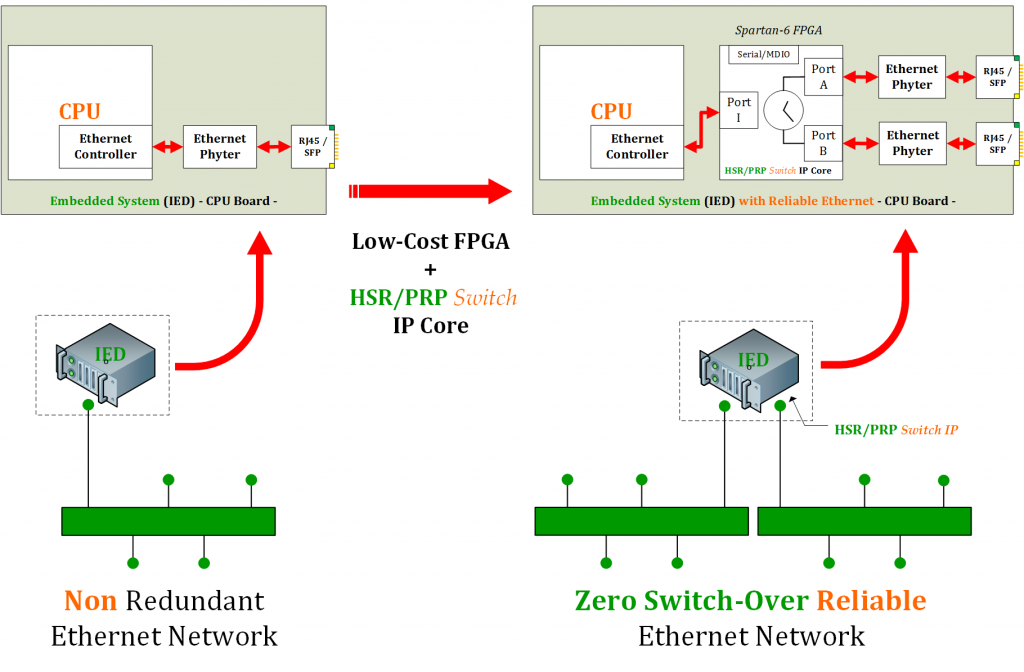

HSR/PRP交換機IP內核是一款硬體解決方案,支援IEC 62439-3標準中的HSR和PRP協議,可在低成本FPGA上實現高可用性無縫冗餘。適用於能源市場自動化設備,該內核提供高速乙太網數據交換,支持多種介面及IEEE 1588時間同步,確保網路的高可靠性與性能優化,並可輕鬆整合至Xilinx FPGA設計中。

Category: Wireless Communication Tags: FPGA IP內核, HSR/PRP Switches, IEC 62439-3, IP Core, Xilinx Vivado支援, 冗餘網路設計, 無縫冗餘, 高可用性乙太網

Description

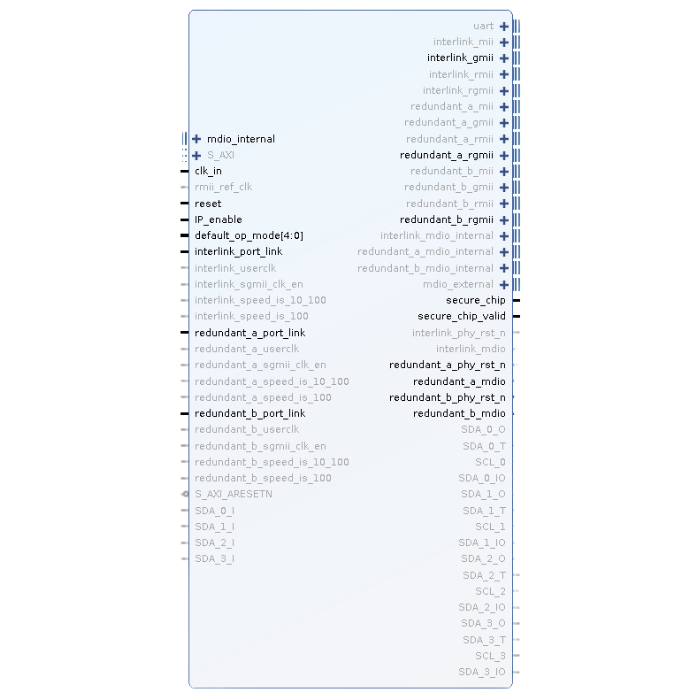

connector

- 它通過硬體交換幀。此功能提供了很高的交換速度,是實現變電站自動化的過程匯流排和機架間匯流排的最大允許使用年限和資料完整性所必需的

- 處理體系結構專用於HSR/PRP。千兆乙太網的轉發延遲為500ns

- 它是一種全硬體。無需片上微處理器或軟體堆疊

- 它已經過優化,幾乎不需要邏輯資源,從而可以在低成本FPGA器件上實現

- Giant Frame Management

exchange

- Dynamic MAC table with automatic MAC address learning and aging (up to 2048 entries)

- Static MAC table (up to 2048 entries)

- Giant Frame Management

- Exchange based on the ethernet

- Entrance Port Mirror

- Broadcast/Multicast Storm Protection

- Rate limiting per port (broadcast, multicast and unicast traffic)

Time Synchronization

- 它支持與SoC-e 1588 IP內核結合的IEEE 1588-2008 v2

組態

- MDIO、UART、AXI4-Lite或CoE(乙太網配置)管理介面

- Configuration over Ethernet (COE): full access to internal registers via the same Ethernet link to the CPU

- 購買IP Core 時提供驅動程式

可定制功能,以優化資源/功能權衡

- 節點表大小

- 每個端口的轉發佇列大小獨立

- 冗余和互連端口中的IEEE1588v2 P2P透明時鐘

- 可擴展的複製/迴圈丟棄表

- VLAN優先順序支持

- 通過AXI4-Lite、MDIO、UART或CoE(乙太網配置)訪問內部寄存器

- 具有整合SAN代理的RedBox模式

- IEEE 1588v2普通時鐘、混合時鐘和邊界時鐘

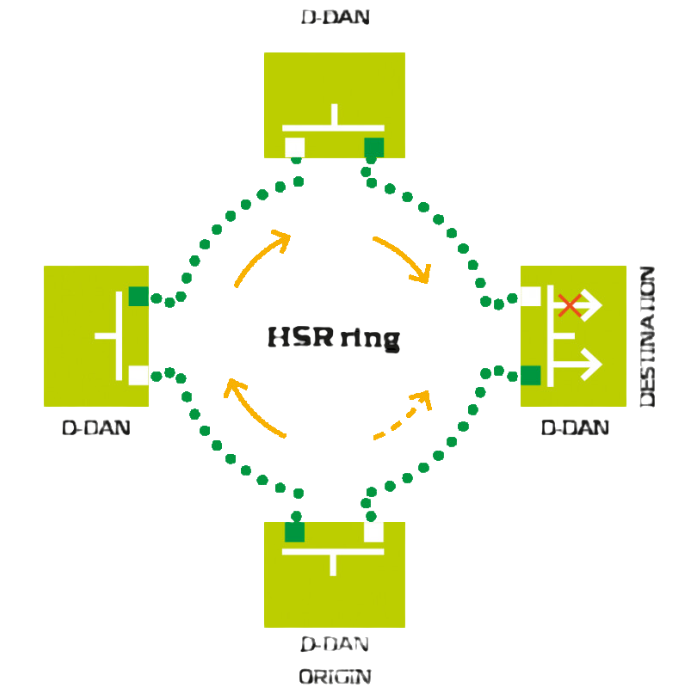

redundancy

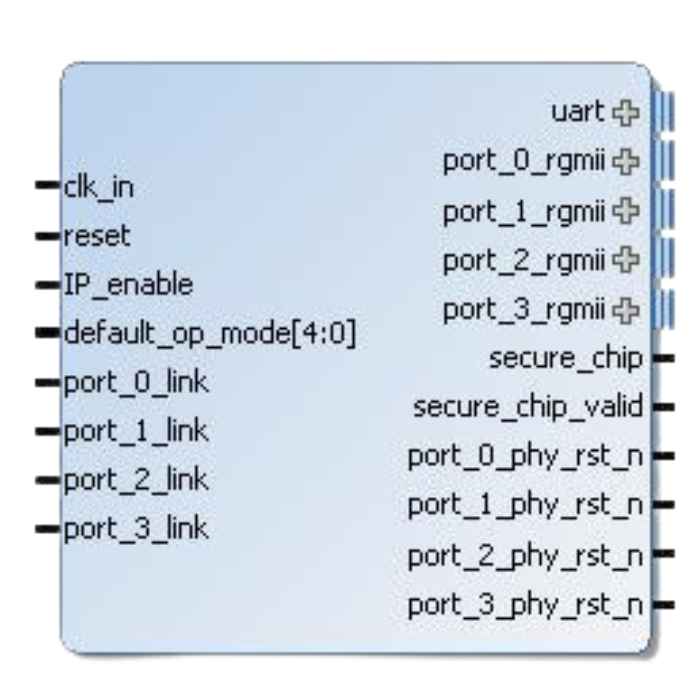

- 它可用於實現終端節點DAN、RedBox或QuadBox功能

- 它帶有單個標誌,可以通過軟體在PRP和HSR模式之間切換

- 它包括整合的每個端口的完整統計資訊和錯誤寄存器(網路監督)

- HSR-HSR,HSR-PRP支援的模式用於無縫PRP-HSR網路合併和Quadbox操作

- VLAN支持和HSR環ID

- SNMP和MIB表可用

– 非冗餘網路的 3 個端口參考與零丟包可靠網路的 3 個端口參考-

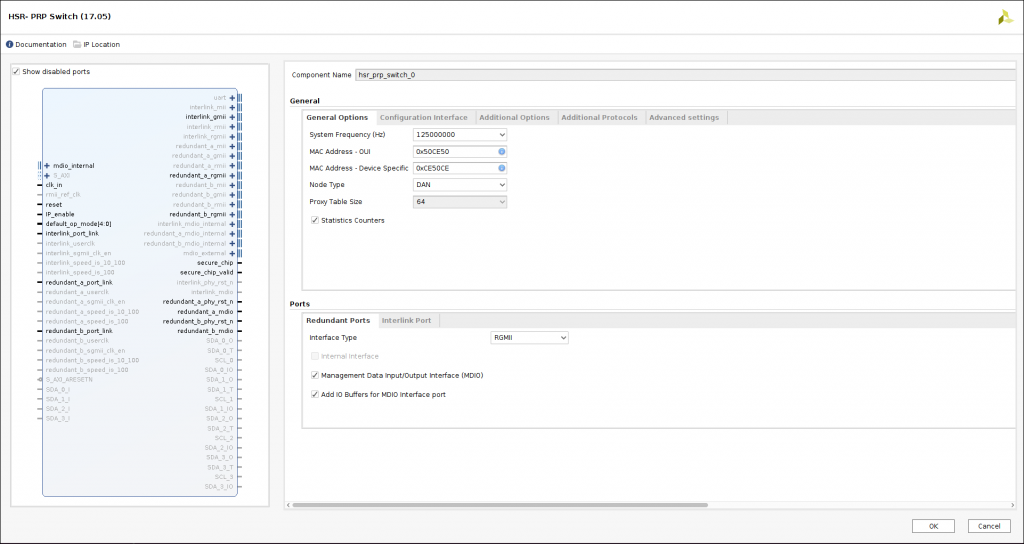

可用於Xilinx Vivado工具的HSR/PRP交換機IP內核

通過利用新的Xilinx Vivado工具,HPS可以輕鬆整合到你的FPGA設計中,該工具允許在圖形化使用者介面中使用該IP內核,並以簡便的方式配置IP參數。

以下Xilinx FPGA系列支援HPS:

- 7-Series (Zynq, Spartan, Artix, Kintex, Virtex)

- Ultrascale (Kintex, Virtex)

- Ultrascale+ (Zynq MPSoC, Kintex, Virtex)

- Versal ACAP