1G MRS - Efficient Redundant Switch IP Core Solution

Function Overview:

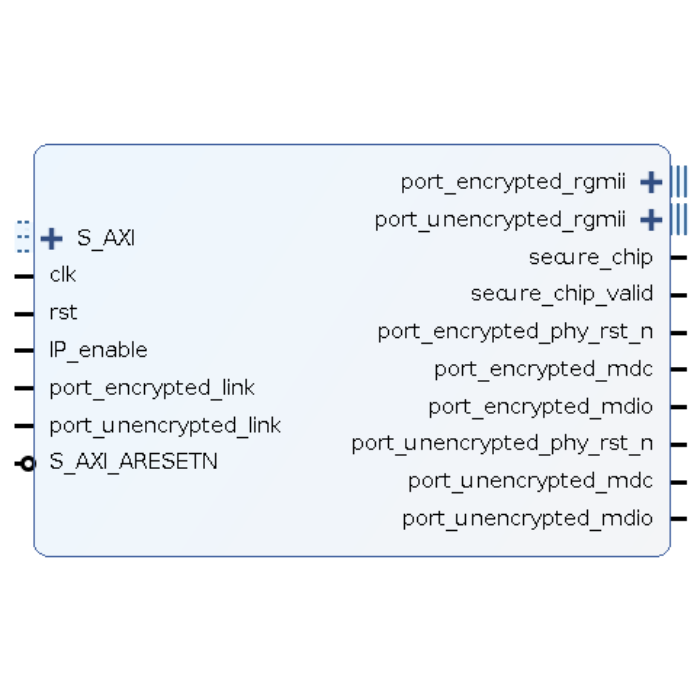

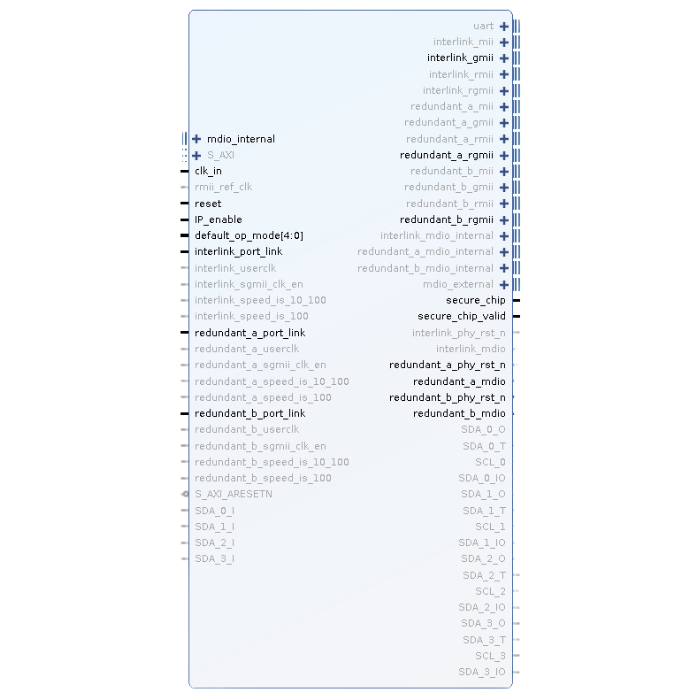

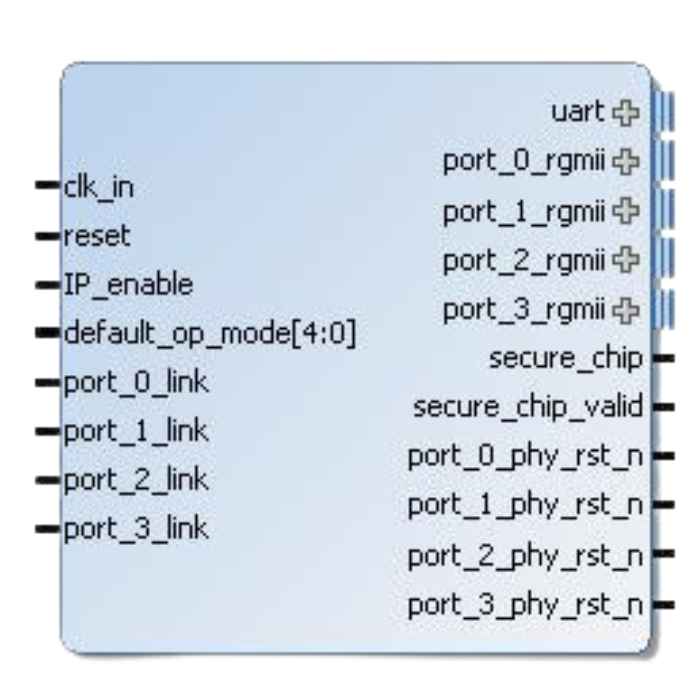

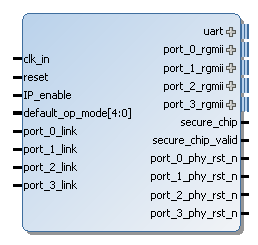

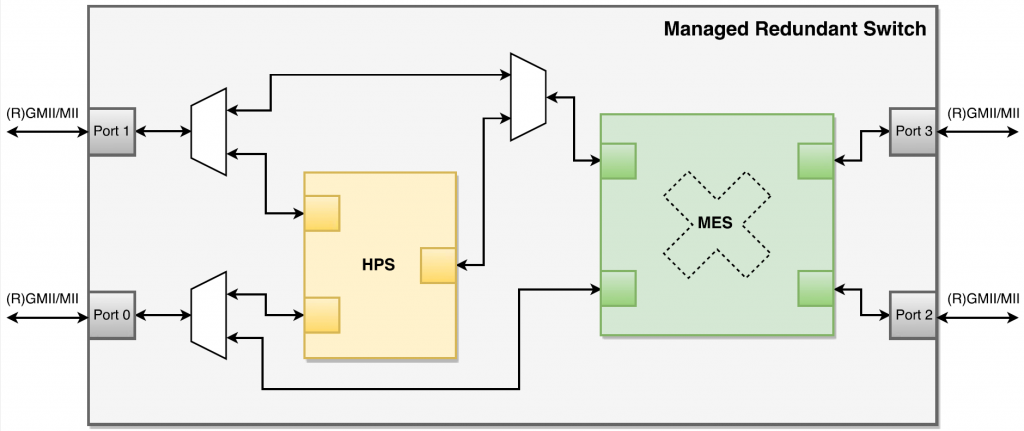

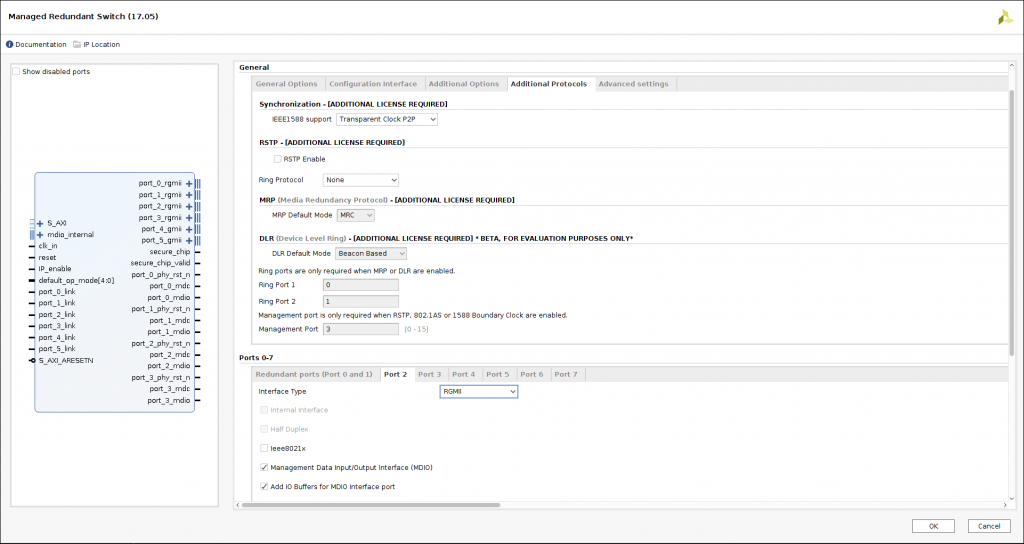

The 1G MRS (Managed Redundant Switch IP core) is a combination of SoC-e HSR-PRP switch (HPS) and Managed Ethernet Switch (MES) IP cores designed for industrial applications. It features automatic MAC learning, VLAN support, QoS management, and support for multiple redundancy protocols (e.g., HSR, PRP, RSTP, MRP, etc.) to ensure high reliability and security for high-speed data transmission. The MRS IP cores are available in a variety of Xilinx FPGA families (e.g., 7-Series, Ultrascale, Versal, etc.). Using Xilinx Vivado tools, users can quickly configure and deploy the IP core to optimize network performance and improve overall system stability and scalability, making it an ideal solution for modern industrial automation, transportation, energy, and other fields.