Precision Time Base is an IEEE1588-2008 v2 compatible clock synchronization IP core for Xilinx FPGAs. It accurately time stamps IEEE 1588 messages and provides a compatible timer. All these processes are performed by the hardware module.

Precision Time Base IP contains elements:

- Hardware Time Stamp Unit (TSU): Can accurately time stamp IEEE 1588 event messages and provides an adjustable timer with sub-microsecond accuracy.TSUs are available in two versions: the PTB TSU and the PTBLite TSU.

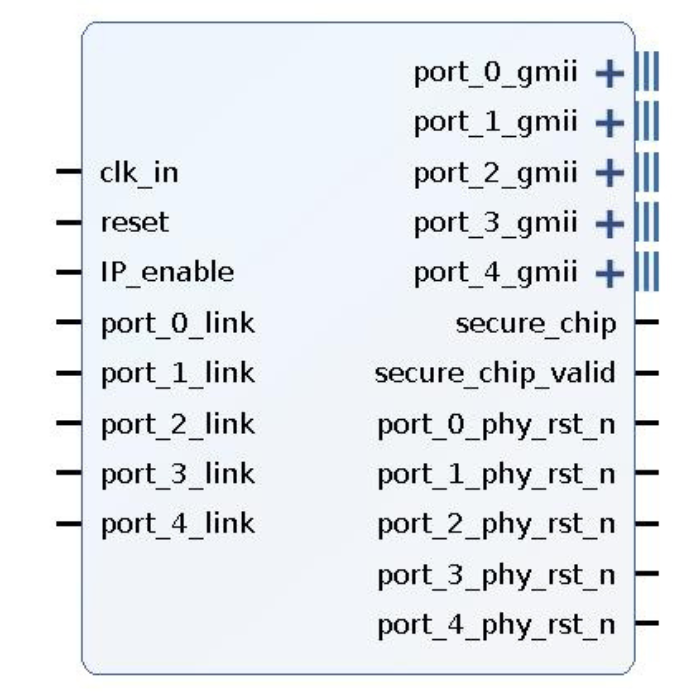

- PTB TSU: Designed as a medium independent interface ([G] MII) connected between the MAC and the PHY, it parses all Ethernet frames and checks which ones are IEEE 1588.

- PTBLite TSU: Utilizes the PTP parser in the Zynq GMAC to provide TSUs with fewer FPGA resources, with some limitations.

- Both versions of the TSU can use an internal adjustable timer or obtain the timer value from another TSU, allowing multiple Ethernet connections to share the same timer.

Software PTP reference design:

The SoC-e provides a Linux kernel patch that allows access to the TSU using the Linux PTP Hardware Clock (PHC) subsystem, and a modified version of the open-source Linux PTP software stack, which is modularized for easy portability.

Supported Xilinx FPGA families:

- 7-Series (Zynq SoC, Spartan, Artix, Kintex, Virtex)

- Ultrascale (Kintex, Virtex)

- Ultrascale+ (Zynq MPSoC, Kintex, Virtex)

- Versal ACAP

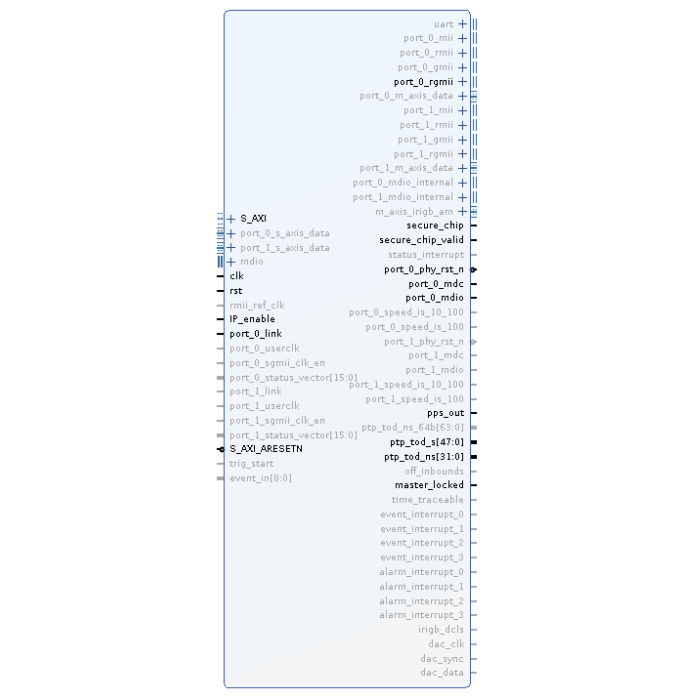

Integration into FPGA designs is made easy with the Xilinx Vivado tool, which allows IP cores to be used in a graphical user interface and IP parameters to be easily configured.

The main function of the Precision Time Base IP Core:

Hardware Features:

- Supports 10/100/1000Mbps/AXI-Stream (for 10Gbps/25Gbps) Interface

- 32-bit Seconds/32-bit Nanoseconds Counter

- 32-bit sub-nanosecond frequency tuning

- One pulse per second output

- Selectable frequency output (1 KHz/2 KHz/4 KHz/8 KHz/16 KHz/32 KHz)

- Lowest FPGA resource utilization

- Alarm Generation

- Event Timestamp Record

Software function:

- General Clock (Master and Slave) Operation

- End-to-end and point-to-point delay mechanism support

- Supports PTP over Ethernet (Layer 2) and IPv4 (Layer 3) interfaces.

- VLAN Support

- Can be used in conjunction with HSR-PRP and managed Ethernet IP kernel.

Profile support:

- Industrial Profiles: Preset, Power, Power Utility IEC 61850-9-3, IEEE 802.1AS

- Car Profile: IEEE 802.1AS Generalized PTP (gPTP) Profile

- Enterprise Profile/5G/Telecom Profile: G.8265.1, G.8275.1 and G.8275.2

The ultimate accuracy of an IEEE 1588 system depends on a number of factors, including the local clock frequency, the location of the time stamp in the data chain, etc. The following graph demonstrates the PPS measurement error between a commercial Grandmaster device and the Zedboard Avnet Devopment Platfrom. The following graphic demonstrates the PPS measurement error between a commercial Grandmaster device and a Zedboard Avnet Devopment Platfrom using the Precision Time Base for hardware-assisted time stamping (+/-50 ns).