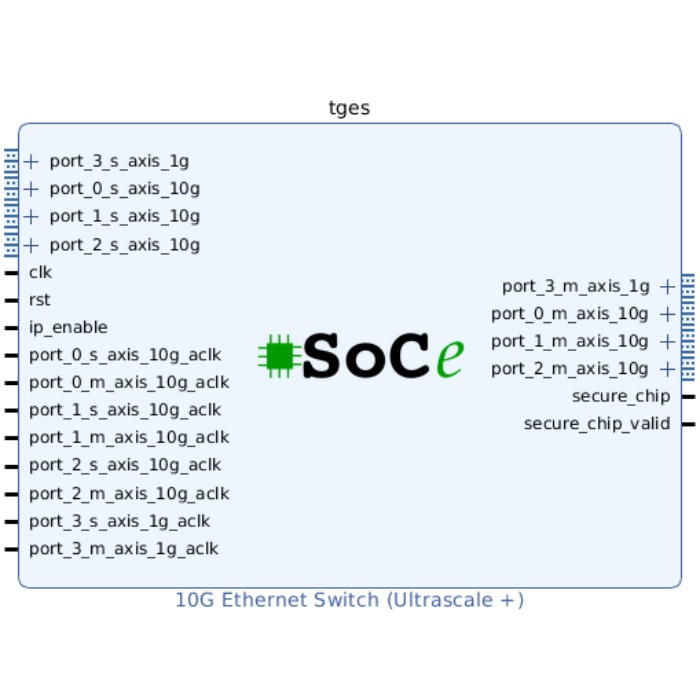

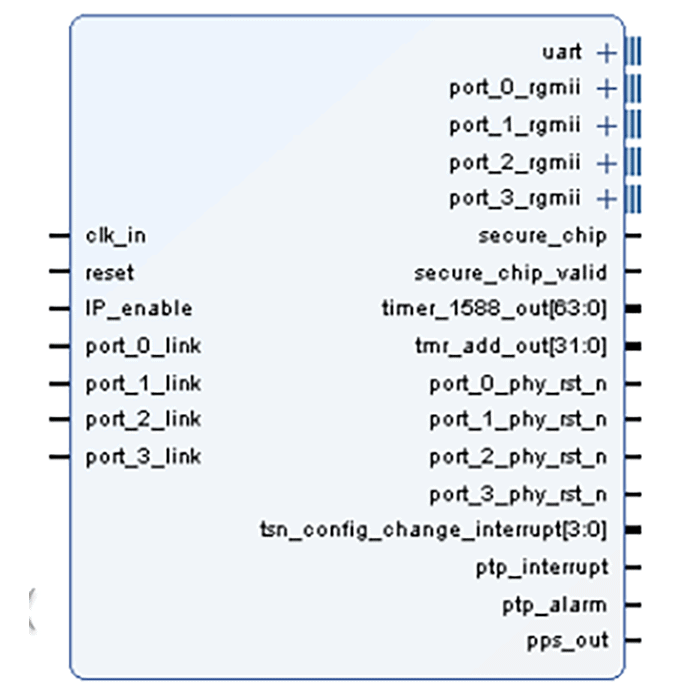

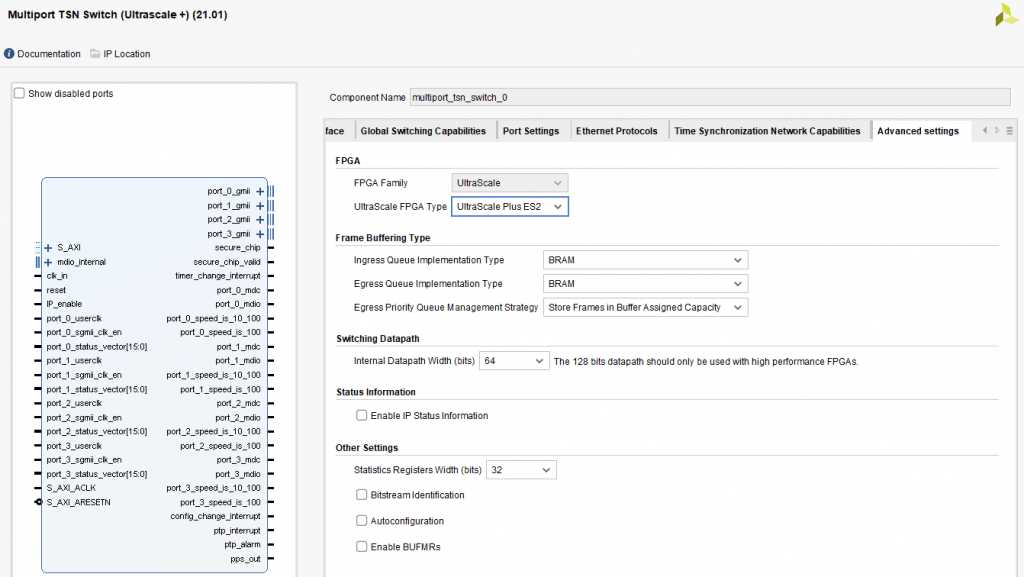

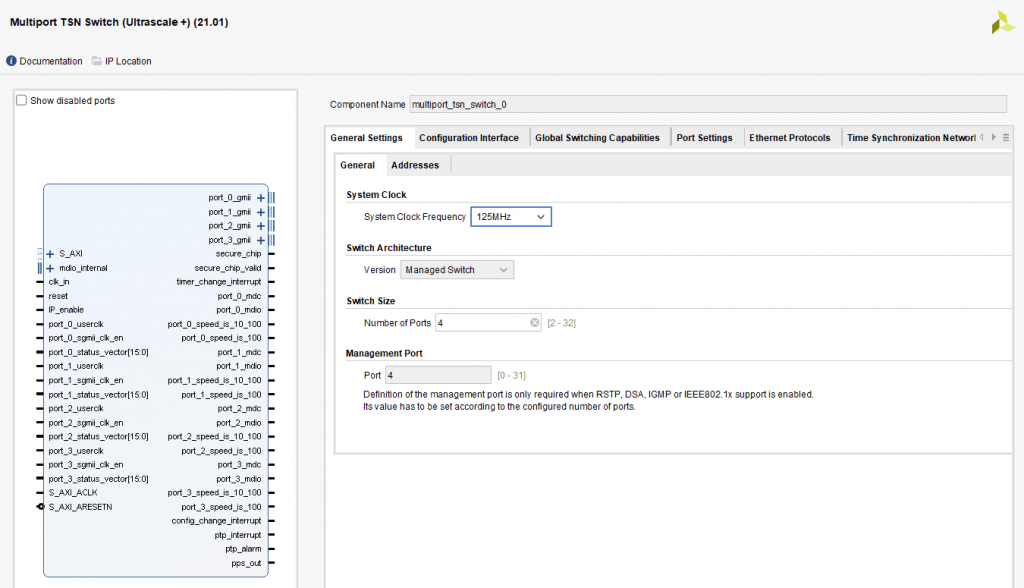

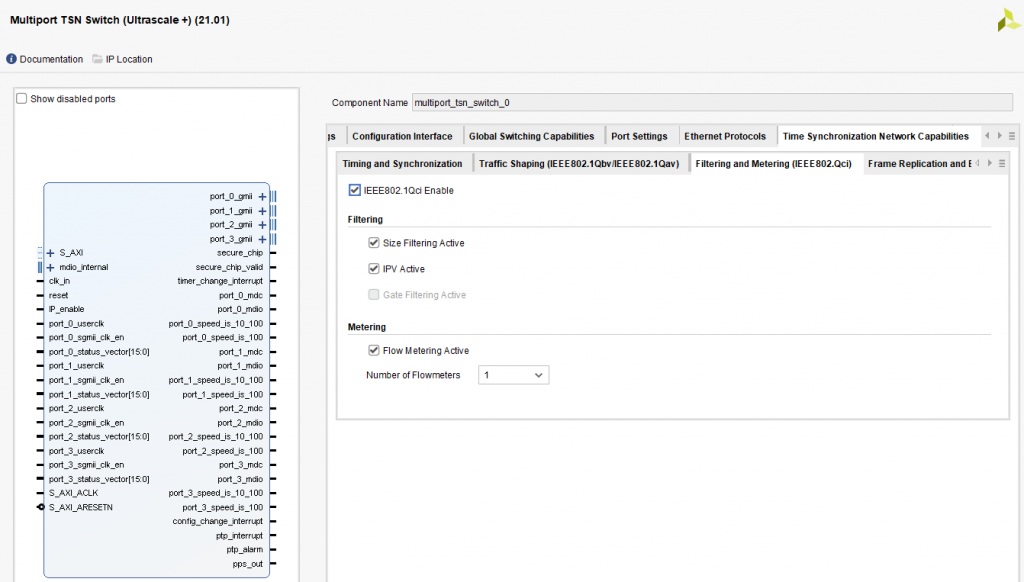

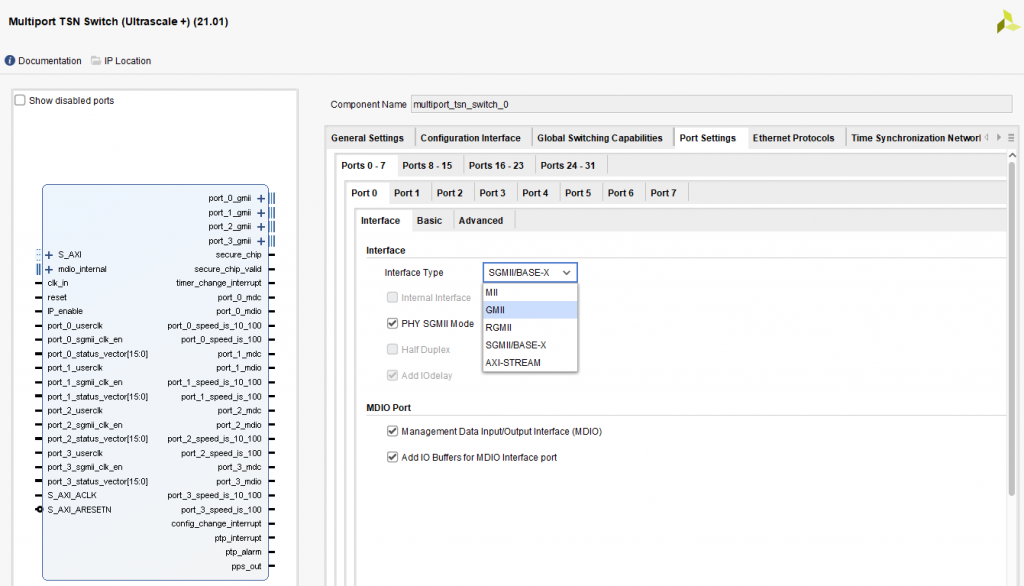

1G MTSN Switch IP Core - Multi-Port TSN Time Sensitive Networking Solution

Function Overview:

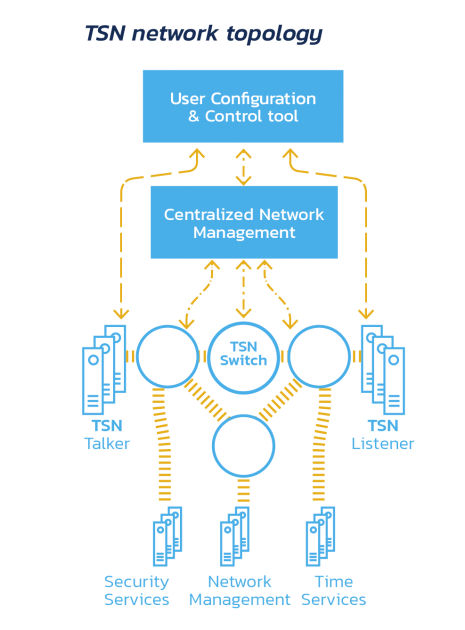

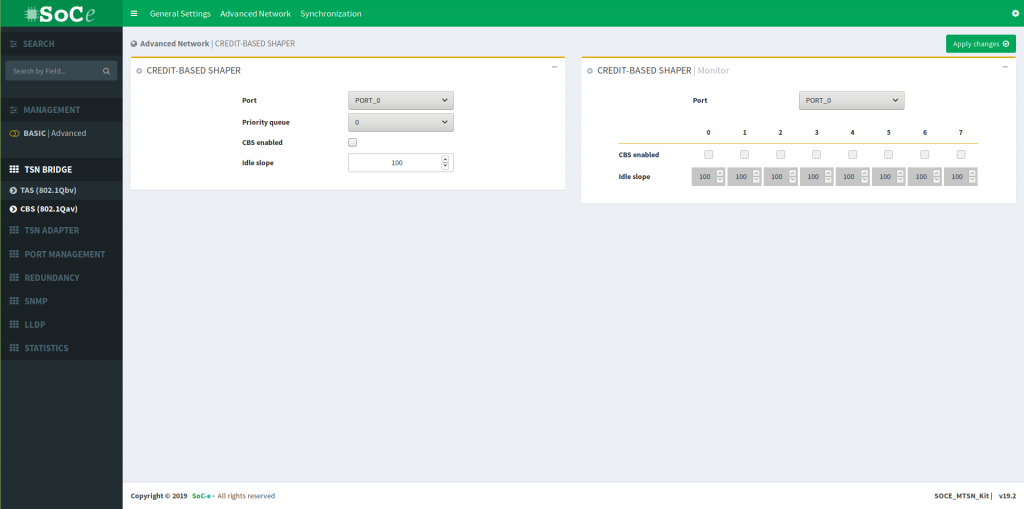

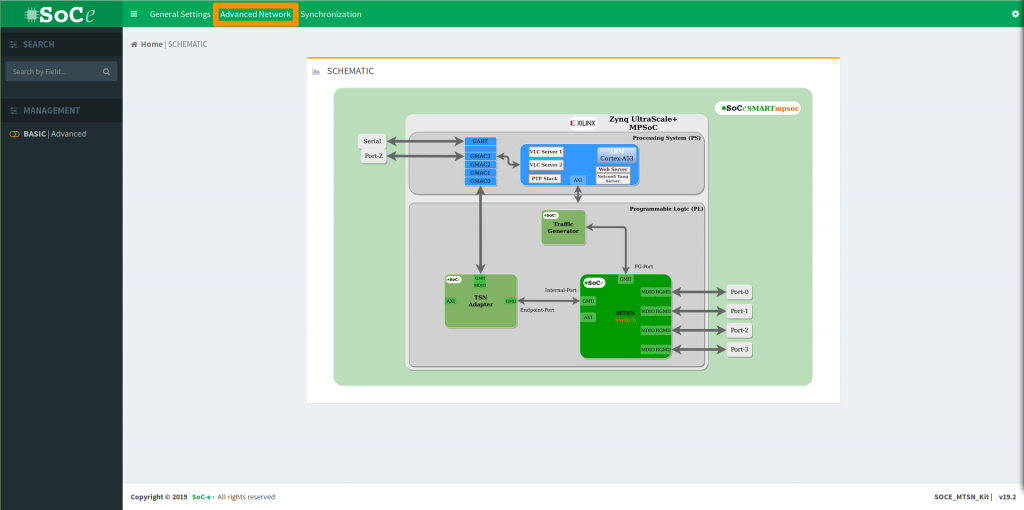

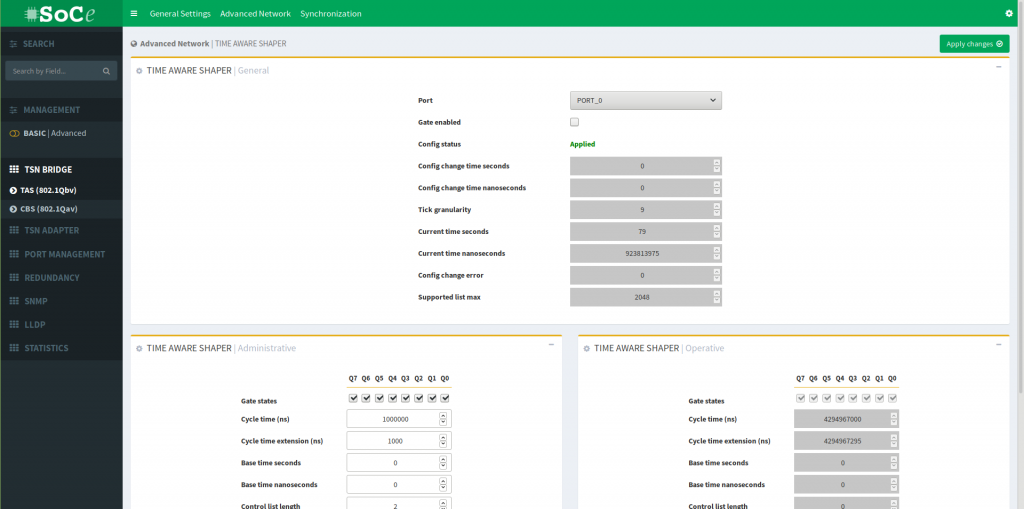

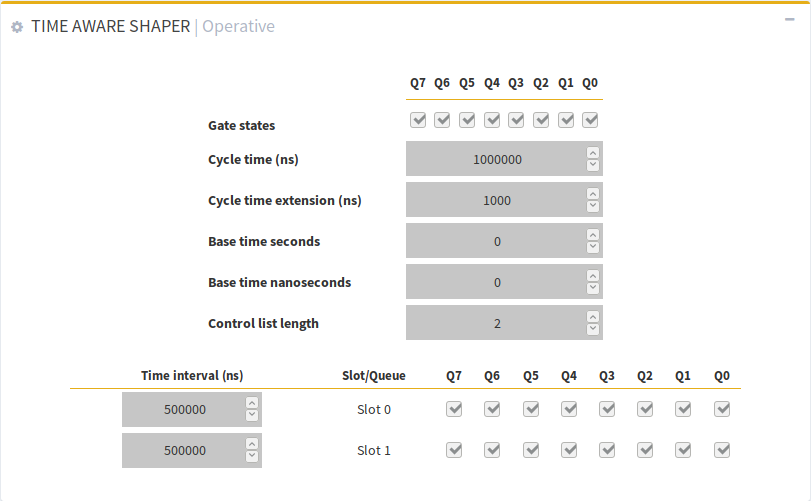

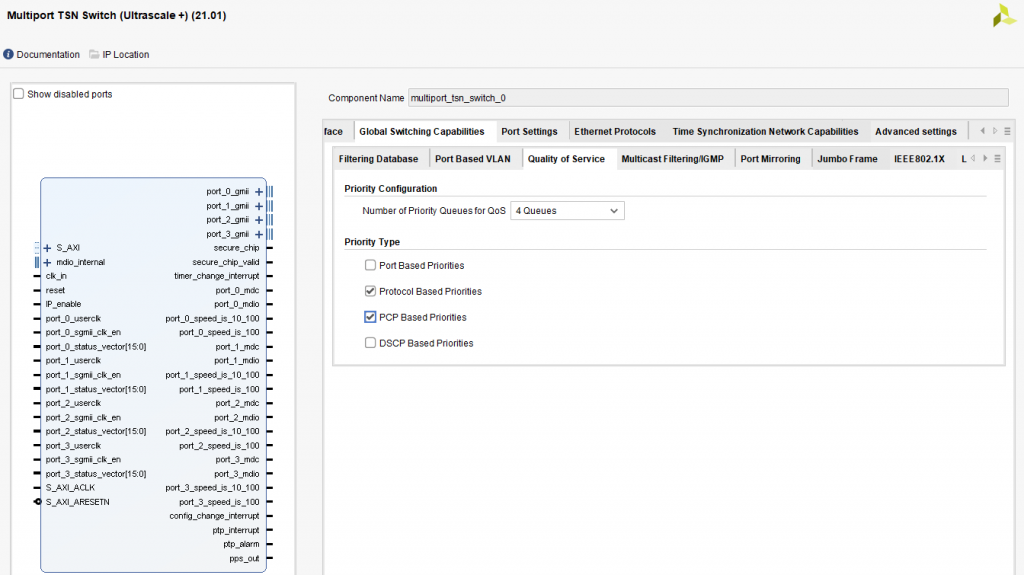

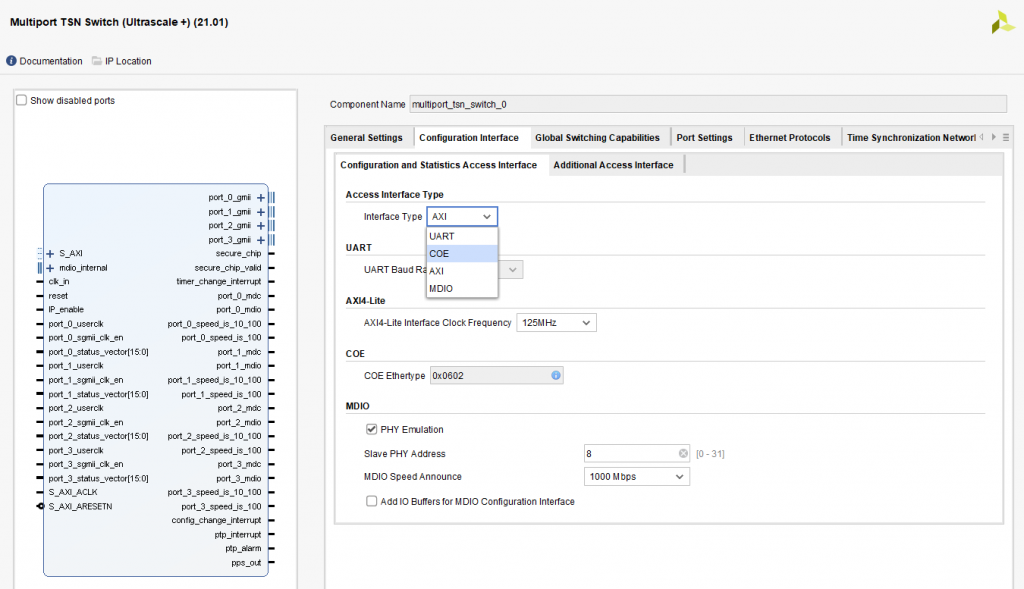

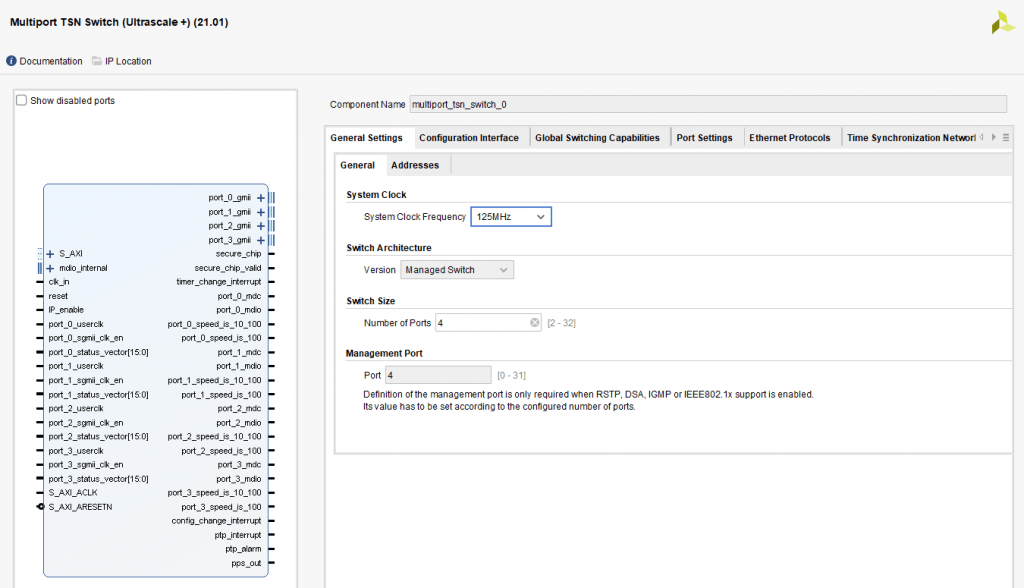

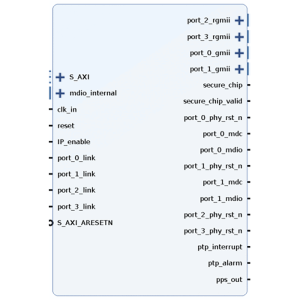

The 1G MTSN Switch IP Core is a multi-port solution designed for Time Sensitive Networks (TSN), supporting 10/100/1000 Mbps Ethernet rates and providing up to 32 Ethernet ports. By supporting IEEE 802.1 series standards such as AS, Qav, Qbv, etc., the IP Core can be flexibly configured for efficient data transfer and synchronization. It supports the Xilinx FPGA family for broadcast storm protection, VLAN support and time synchronization applications, providing a complete solution for industrial automation and network control systems.