IRIG-B Slave IP Core: Highly Accurate Time Synchronization Solution

Function Overview:

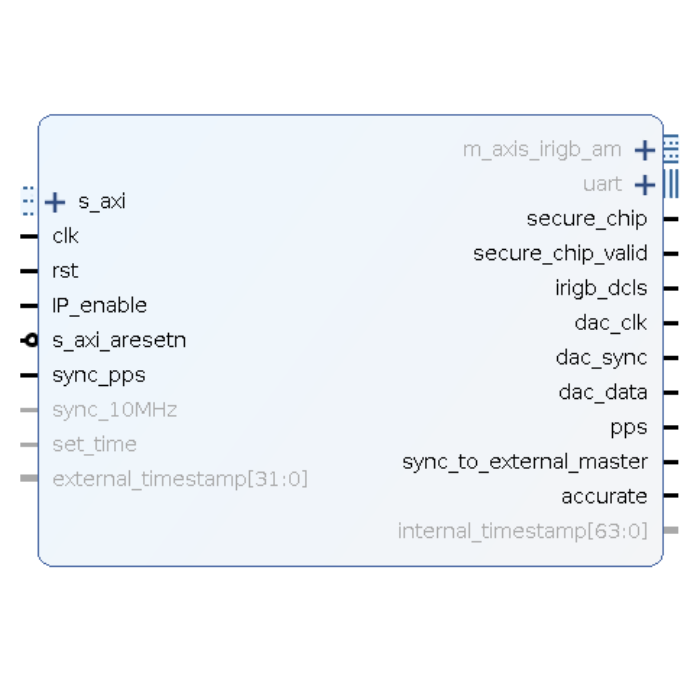

IRIGtimeS is a highly efficient and flexible time synchronization slave IP core designed for compliance with the IRIG 200-04 standard. The IP core supports all IRIG-B encoding algorithms, including DCLS and AM modulation, and is capable of handling seconds, minutes, hours, days and years in time code. The built-in 64-bit internal timer enables sub-microsecond synchronization with IRIG-B masters and provides accurate second and nanosecond timestamps. IRIGtimeS supports multiple Xilinx FPGA families, including 7-Series, Ultrascale, Ultrascale+, and Versal, and can be easily integrated into the Xilinx It can be easily integrated into Xilinx Vivado tools for a wide range of FPGA design projects that require precise time synchronization. The IP cores are designed for autonomy and ease of operation, and provide periodic pulse outputs for test and time synchronization applications.