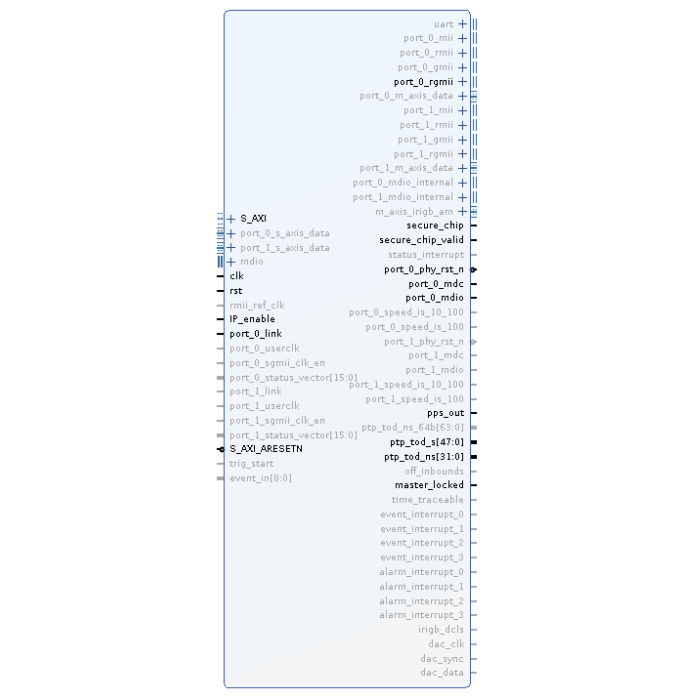

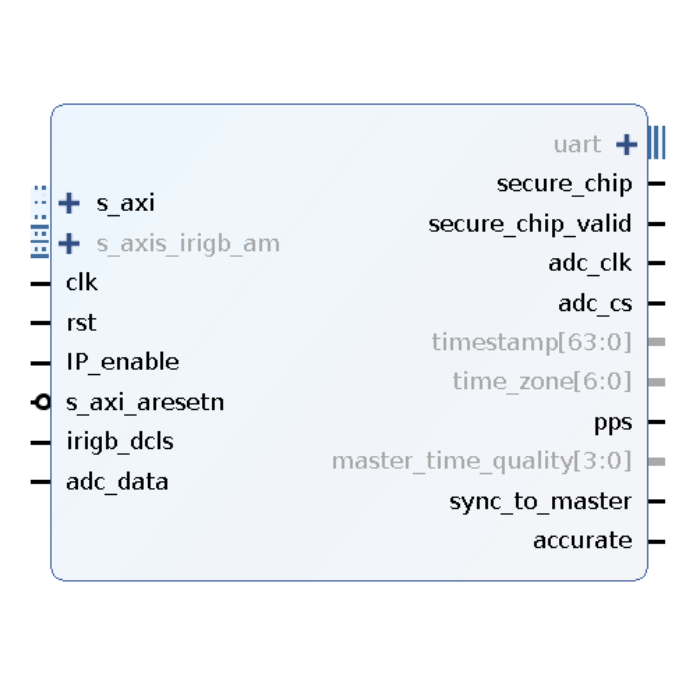

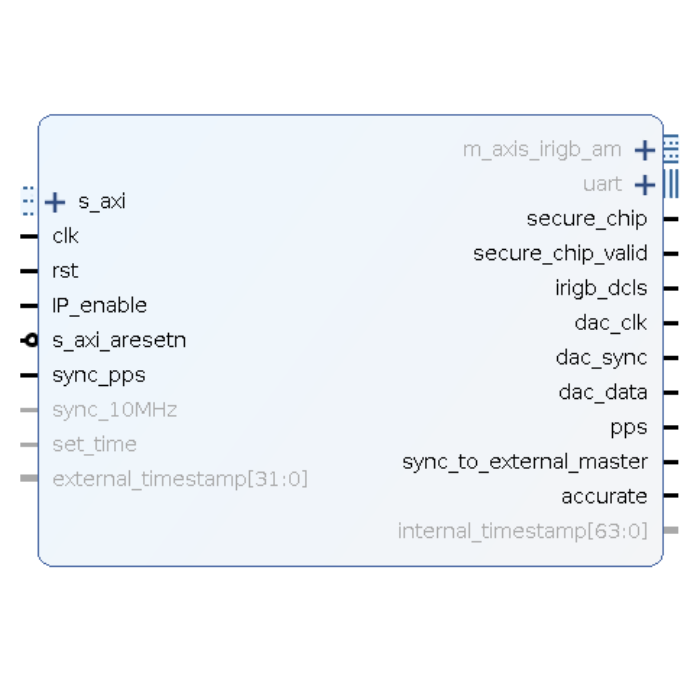

IRIGtimeM An IRIG 200-04 compatible time synchronization master has been implemented on an FPGA device. This IRIG-B master IP is designed to support all IRIG-B encoding algorithms as well as DCLS and AM modulation to provide maximum flexibility.

This IRIG-B master IP generates IRIG-B frames per second, including mandatory and optional time information (seconds, minutes, hours, days, years, control functions, and consecutive binary seconds), depending on the IRIG-B time code selected on the configuration. The IP is capable of supporting autonomous operation without excessive configuration.

Supported Xilinx FPGA families:

- 7-Series (Zynq SoC, Spartan, Artix, Kintex, Virtex)

- Ultrascale (Kintex, Virtex)

- Ultrascale+ (Zynq MPSoC, Kintex, Virtex)

- Versal ACAP

IRIGtimeM can be easily integrated into FPGA designs by integrating it with the managed Ethernet switch IP core of the Xilinx Vivado tool, which allows the IP core to be used in a graphical user interface and IP parameters to be configured in an easy way.

IRIGtimeM Key Features:

- IRIG 200-04 compliant time synchronization masters

- Supports DCLS and AM modulation

- Supports all IRIG-B encoded algorithms, including year information, control functions and continuous binary seconds.

- Output type (IRIG-B time code) can be configured before implementation and during operation

- Precision IRIG-B output for nanosecond accuracy

- 32-bit timestamp input for initial IP settings

- Periodic pulse output for testing