IEEE 1588v2 CPU-less Clock Synchronization Solution - 1588 Tiny IP Core

Function Overview:

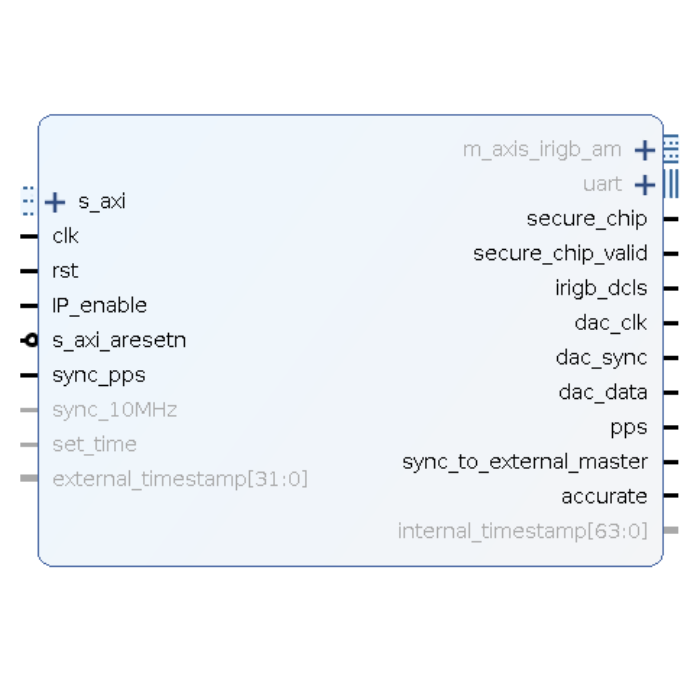

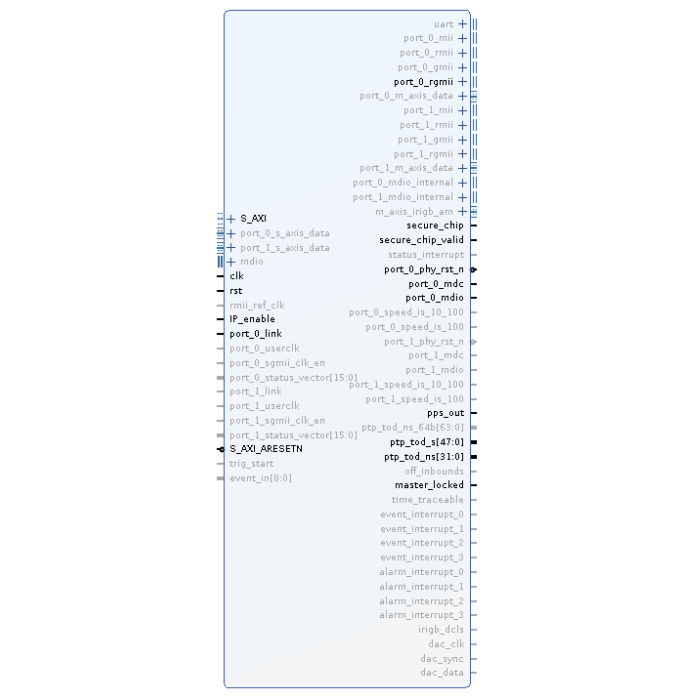

1588 TinyIt is a specializedXilinx FPGAdesignerIEEE 1588-2008 V2Slave hardware clock synchronizationIPKernel. It provides accurate time stamping and clock synchronization without relying on embedded processors or general-purpose Ethernet.MACThe system is designed to provide high efficiency for resource-constrained equipment.IEEE 1588function support. TheIPThe kernel supports a variety of Ethernet interfaces, includingMII、GMII、SGMIIetc., and can handlePTPThe report supports both single- and dual-port modes. It also supports a variety of profiles (such asIEC 61850(for example, power setup files, etc.), for7-Series、Ultrascale、Ultrascale+及Versal ACAP等Xilinx FPGASeries.1588 Tiny與Xilinx VivadoTools are seamlessly integrated, making them easy to configure and integrate into theFPGAThe design ensures that theFPGAHighly accurate hardware time synchronization is performed internally.