10G TSN Switch IP Core - Multi-Port Ethernet Time-Sensitive Network Solution

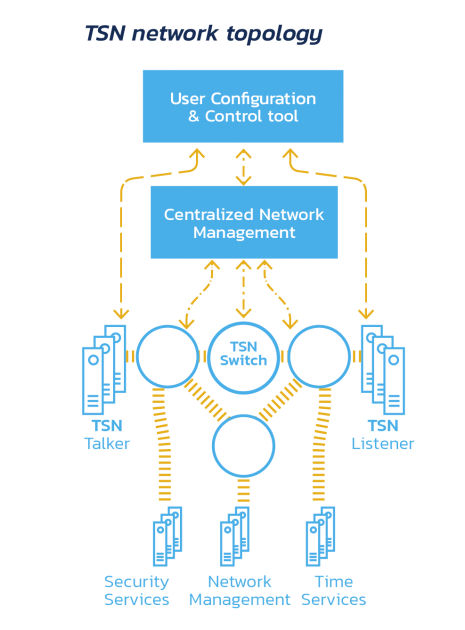

Generate an optimized TSN bridge or endpoint device for your application.

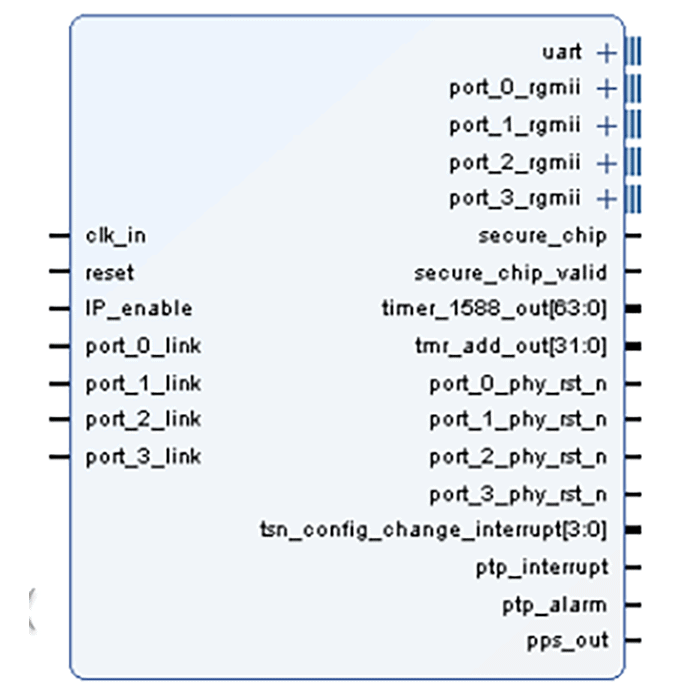

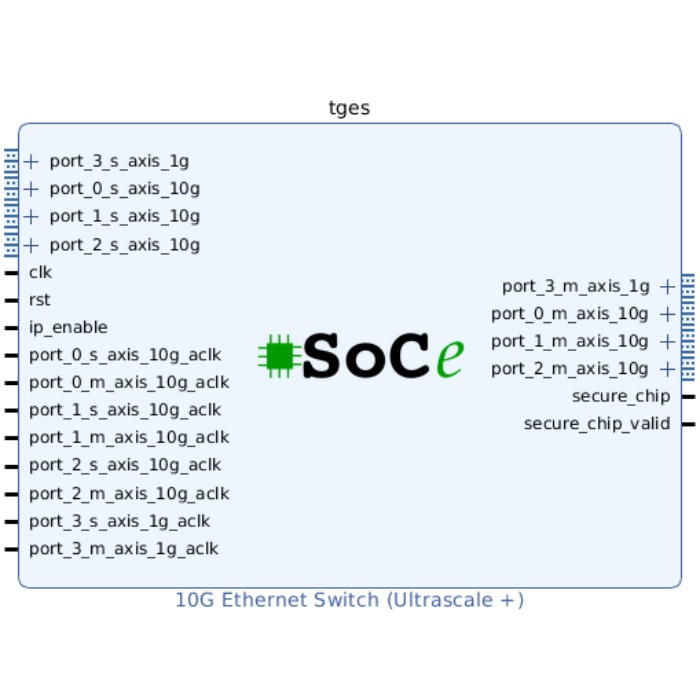

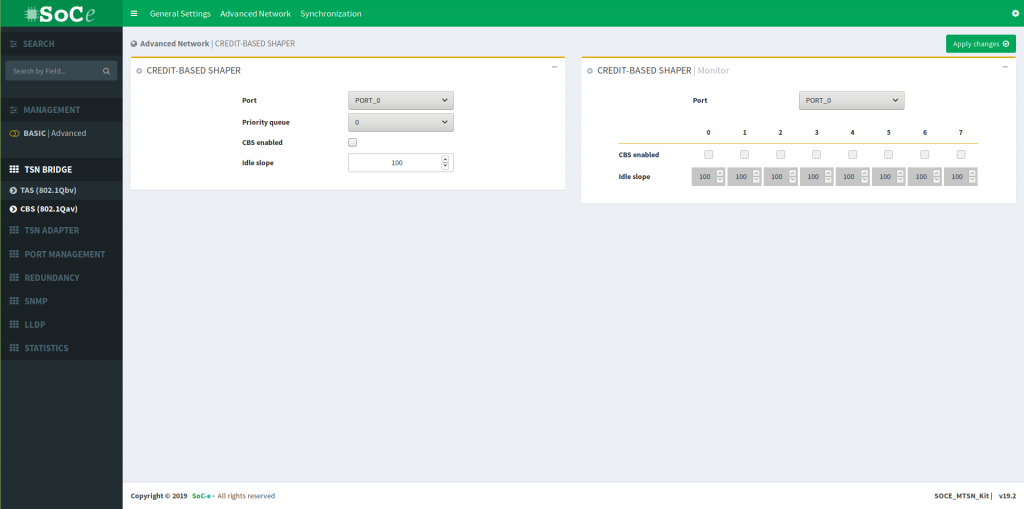

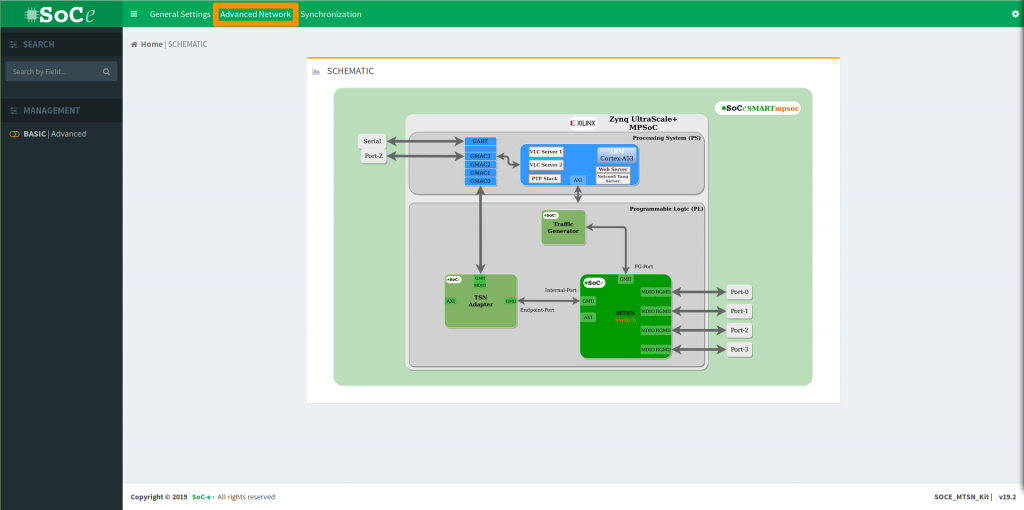

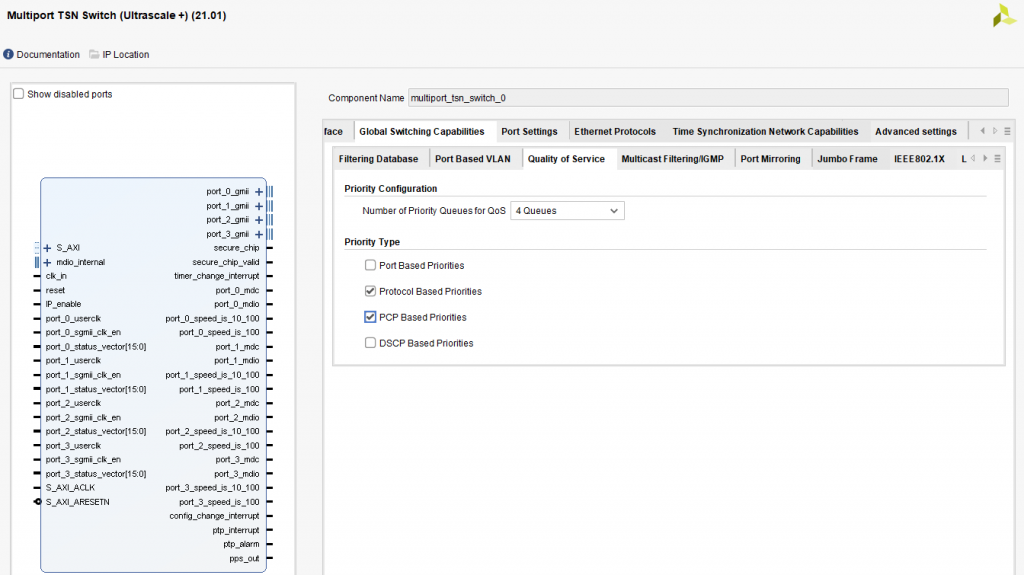

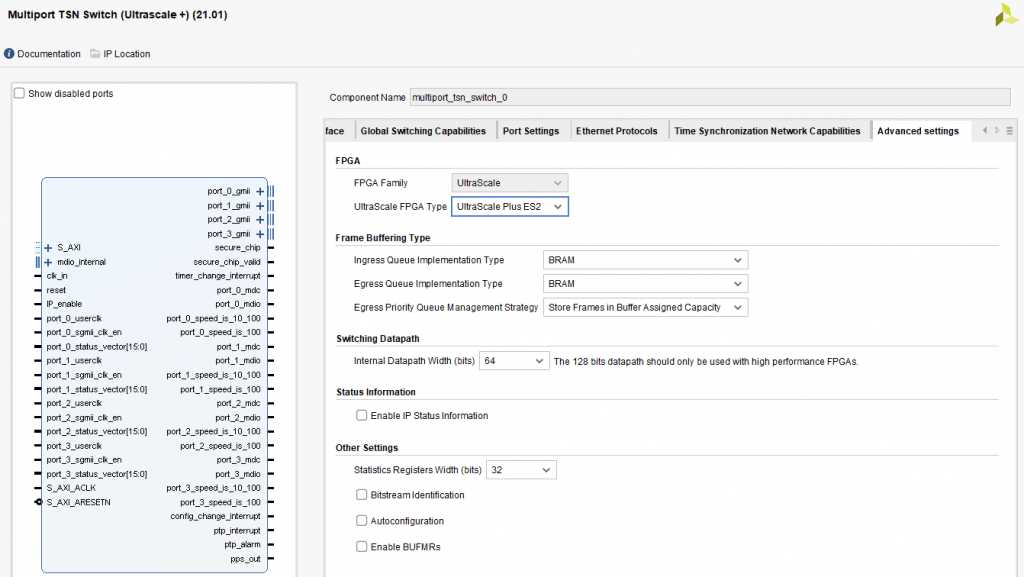

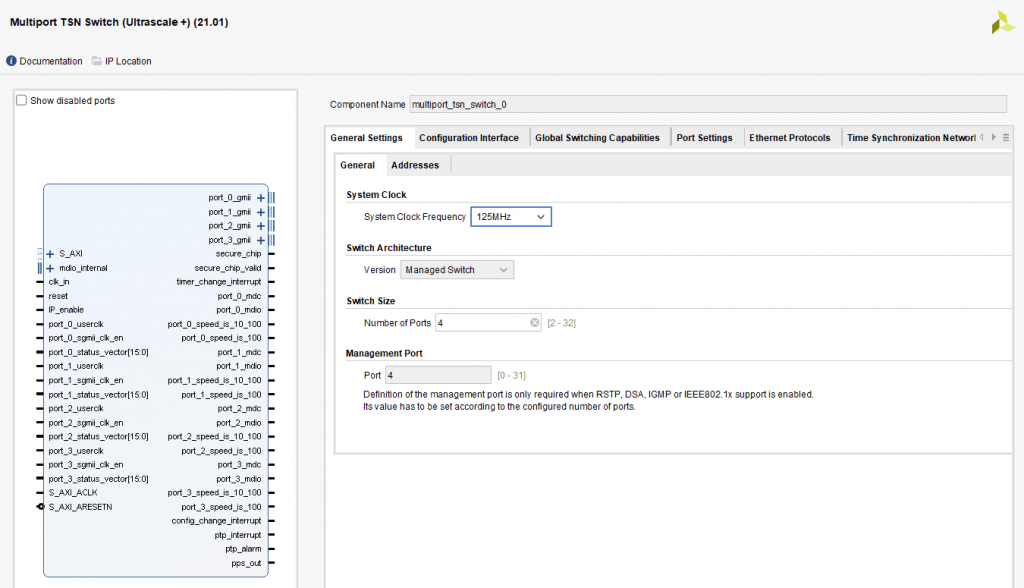

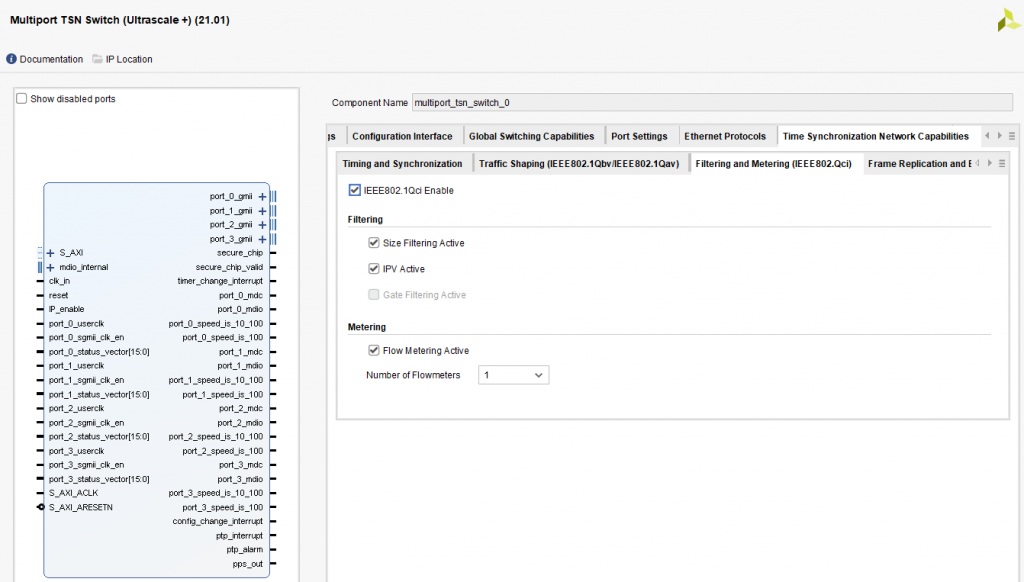

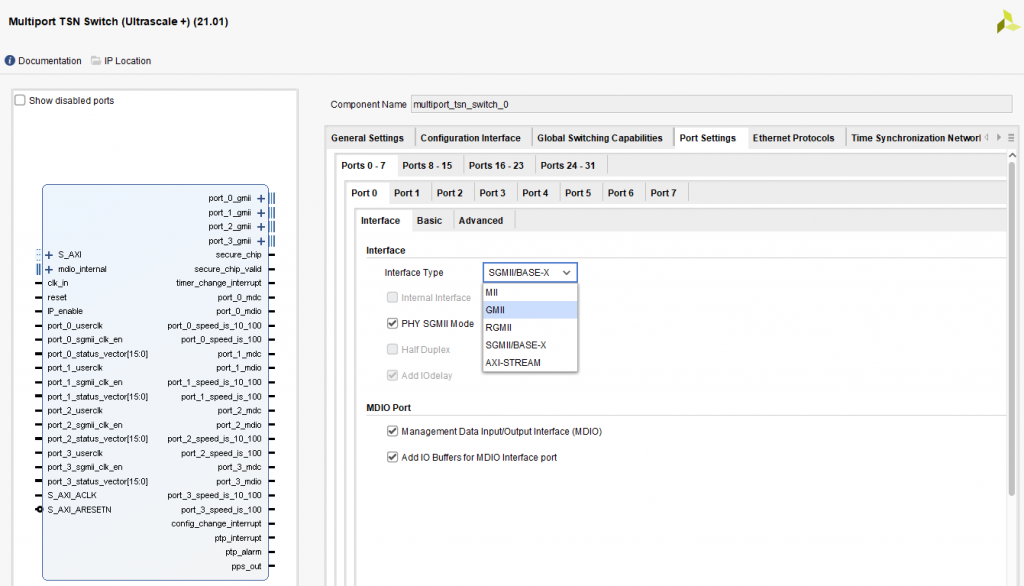

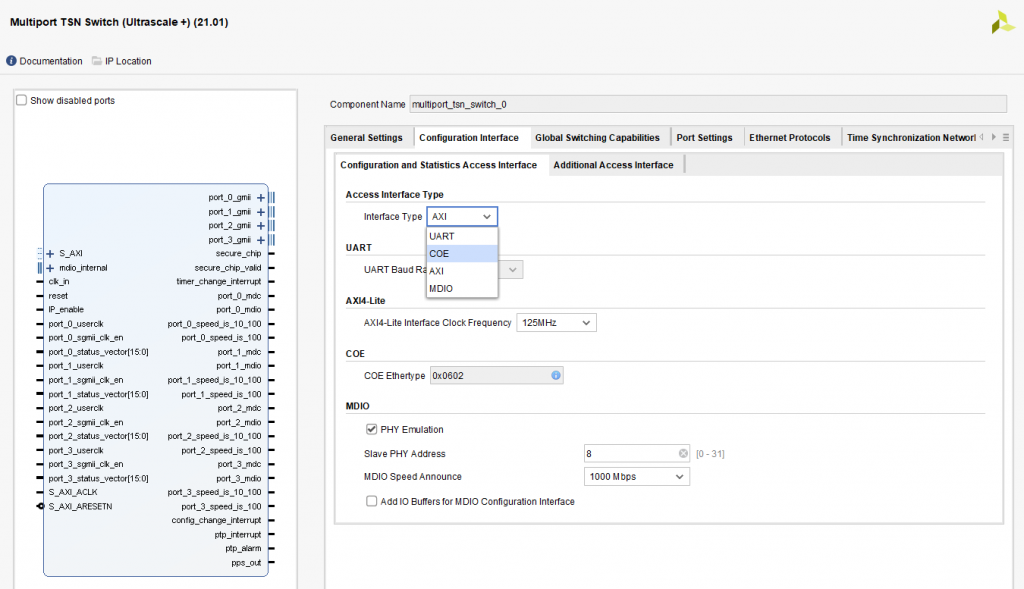

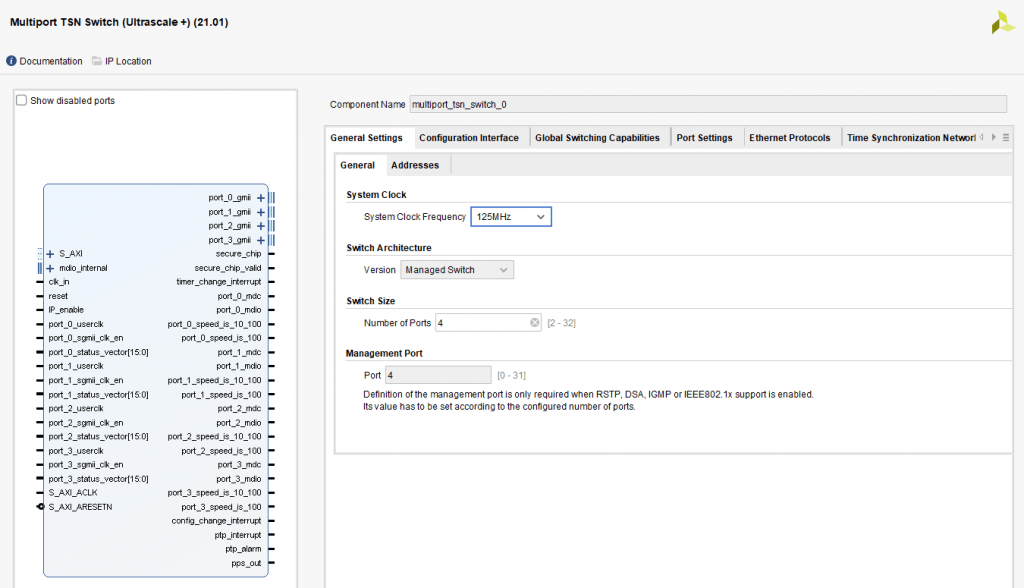

Honghong's new10G TSN Ethernet switch IP nucleus isThe latest version of the MTSN Switch IP core. It is also a flexible HDL code that can generate TSN endpoints or TSN bridge implementations, but optionally with a10G portsAs with other SoC-e IP cores, the IP has a rich set of common parameters for optimal functional resource tradeoffs. Like other SoC-e IP cores, this IP has a rich set of generalized parameters for optimal functional resource tradeoffs. These generalizations can also be configured graphically through the Vivado GUI.